Modifying the example design – Altera Arria V GZ Avalon-ST User Manual

Page 23

Modifying the Example Design

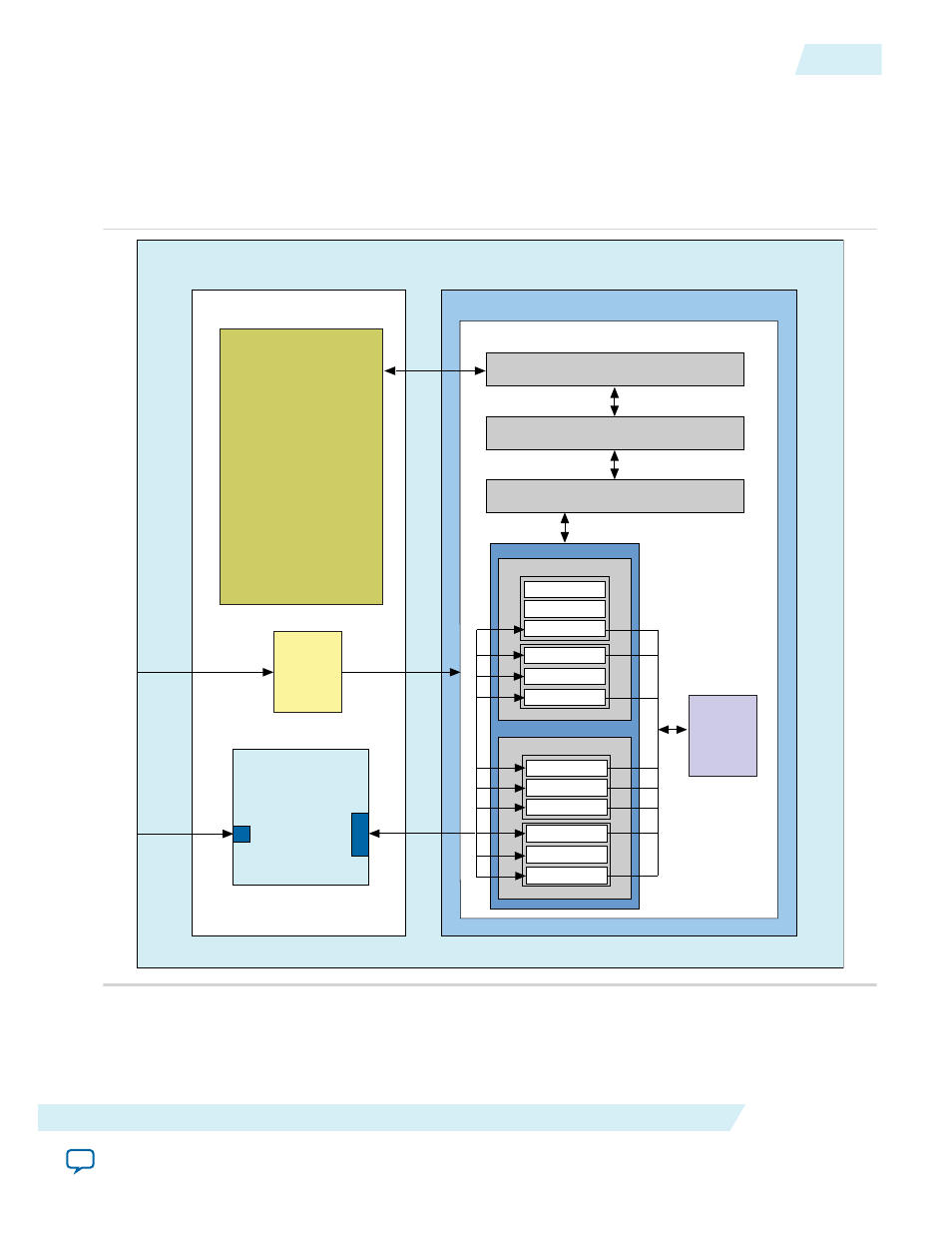

To use this example design as the basis of your own design, replace the Chaining DMA Example shown in

the following figure with your own Application Layer design. Then modify the Root Port BFM driver to

generate the transactions needed to test your Application Layer.

Figure 2-4: Testbench for PCI Express

PCB

Avalon-MM slave

Reset

Hard IP for PCI Express

Altera FPGA

PCB

Transaction Layer

Data Link Layer

PHY MAC Layer

x8 PCIe Link

(Physical Layer)

Lane 7

(Unused)

(Unused)

Lane 6

Lane 5

TX PLL

PHY IP Core for PCI Express

Lane 2

Lane 3

Lane 4

Lane 1

Lane 0

TX PLL

Transceiver Bank

Transceiver Bank

S

Reconfig

to and from

Transceiver

to and from

Embedded

Controller

(Avalon-MM

slave interface)

Transceiver

Reconfiguration

Controller

Root

Port

BFM

npor

Reset

APPS

DUT

Chaining DMA

(User Application)

UG-01127_avst

2014.12.15

Modifying the Example Design

2-9

Getting Started with the Arria V GZ Hard IP for PCI Express

Altera Corporation