Altera Arria V GZ Avalon-ST User Manual

Page 71

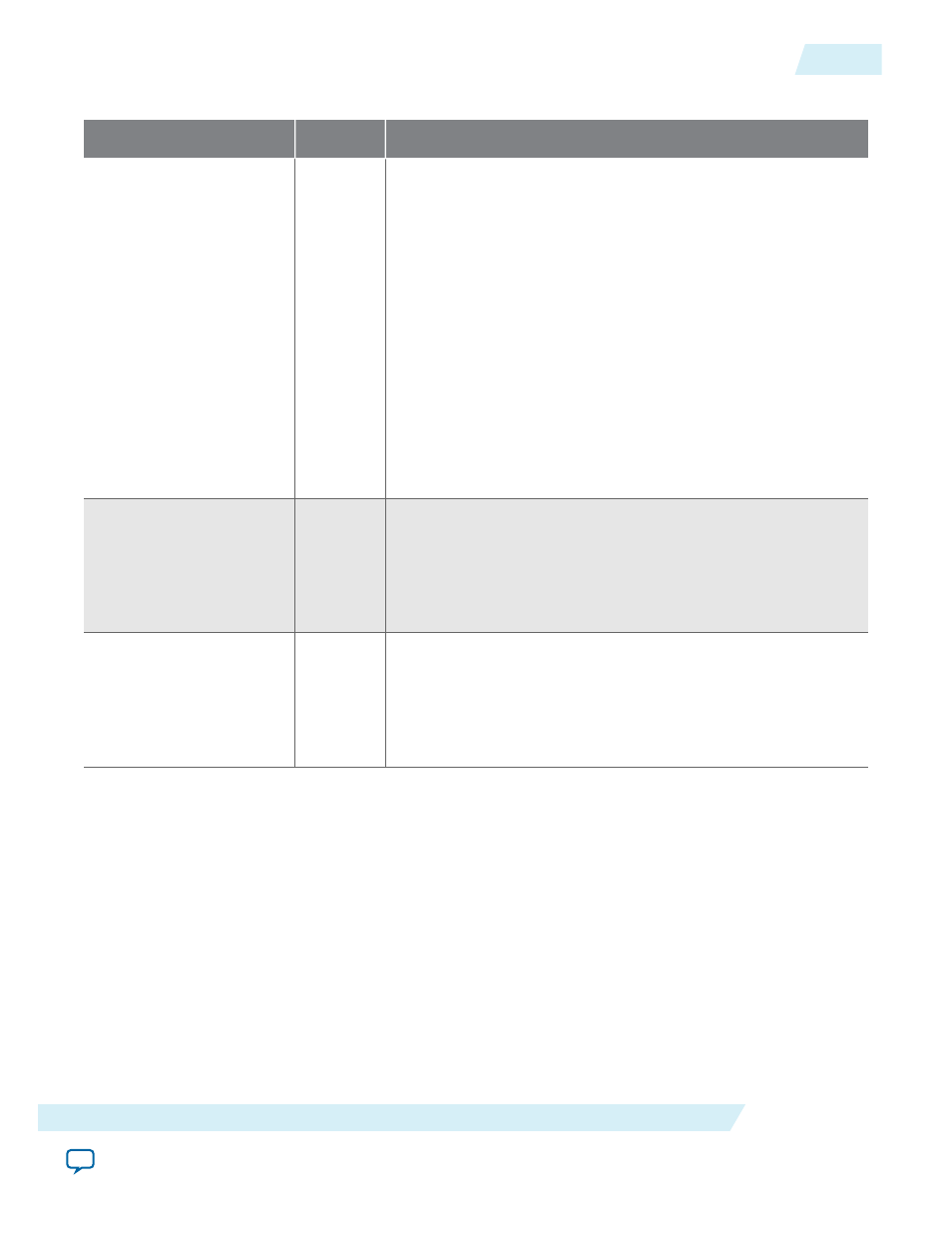

Table 5-4: 64-, 128-, or 256‑Bit Avalon-ST TX Datapath

Signal

Direction

Description

tx_st_data[

Input

Data for transmission. Transmit data bus. Refer to the following

sections on data alignment for the 64-, 128-, and 256-bit

interfaces for the mapping of TLP packets to

tx_st_data

and

examples of the timing of this interface. When using a 64-bit

Avalon-ST bus, the width of

tx_st_d

ata

is 64. When using a

128-bit Avalon-ST bus, the width of

tx_st_data

is 128 bits.

When using a 256-bit Avalon-ST bus, the width of

tx_st_data

is

256 bits. The Application Layer must provide a properly

formatted TLP on the TX interface. The mapping of message

TLPs is the same as the mapping of Transaction Layer TLPs with

4 dword headers. The number of data cycles must be correct for

the length and address fields in the header. Issuing a packet with

an incorrect number of data cycles results in the TX interface

hanging and becoming unable to accept further requests.

tx_st_sop[

Input

Indicates first cycle of a TLP when asserted together with

tx_st_

valid

.

When using a 256-bit Avalon-ST bus with Multiple packets per

cycle, bit 0 indicates that a TLP begins in tx_st_data[127:0], bit 1

indicates that a TLP begins in tx_st_data[255:128].

tx_st_eop[

Input

Indicates last cycle of a TLP when asserted together with

tx_st_

valid

.

When using a 256-bit Avalon-ST bus with Multiple packets per

cycle, bit 0 indicates that a TLP ends with tx_st_data[127:0], bit 1

indicates that a TLP ends with tx_st_data[255:128].

UG-01127_avst

2014.12.15

Avalon-ST TX Interface

5-19

Interfaces and Signal Descriptions

Altera Corporation