Pclk, Coreclkout_hip – Altera Arria V GZ Avalon-ST User Manual

Page 143

As this figure indicates, the IP core includes the following clock domains:

pclk

The transceiver derives

pclk

from the 100 MHz

refclk

signal that you must provide to the device.

The PCI Express Base Specification requires that the

refclk

signal frequency be 100 MHz ±300 PPM.

The transitions between Gen1, Gen2, and Gen3 should be glitchless.

pclk

can be turned off for most of

the 1 ms timeout assigned for the PHY to change the clock rate; however,

pclk

should be stable before the

1 ms timeout expires.

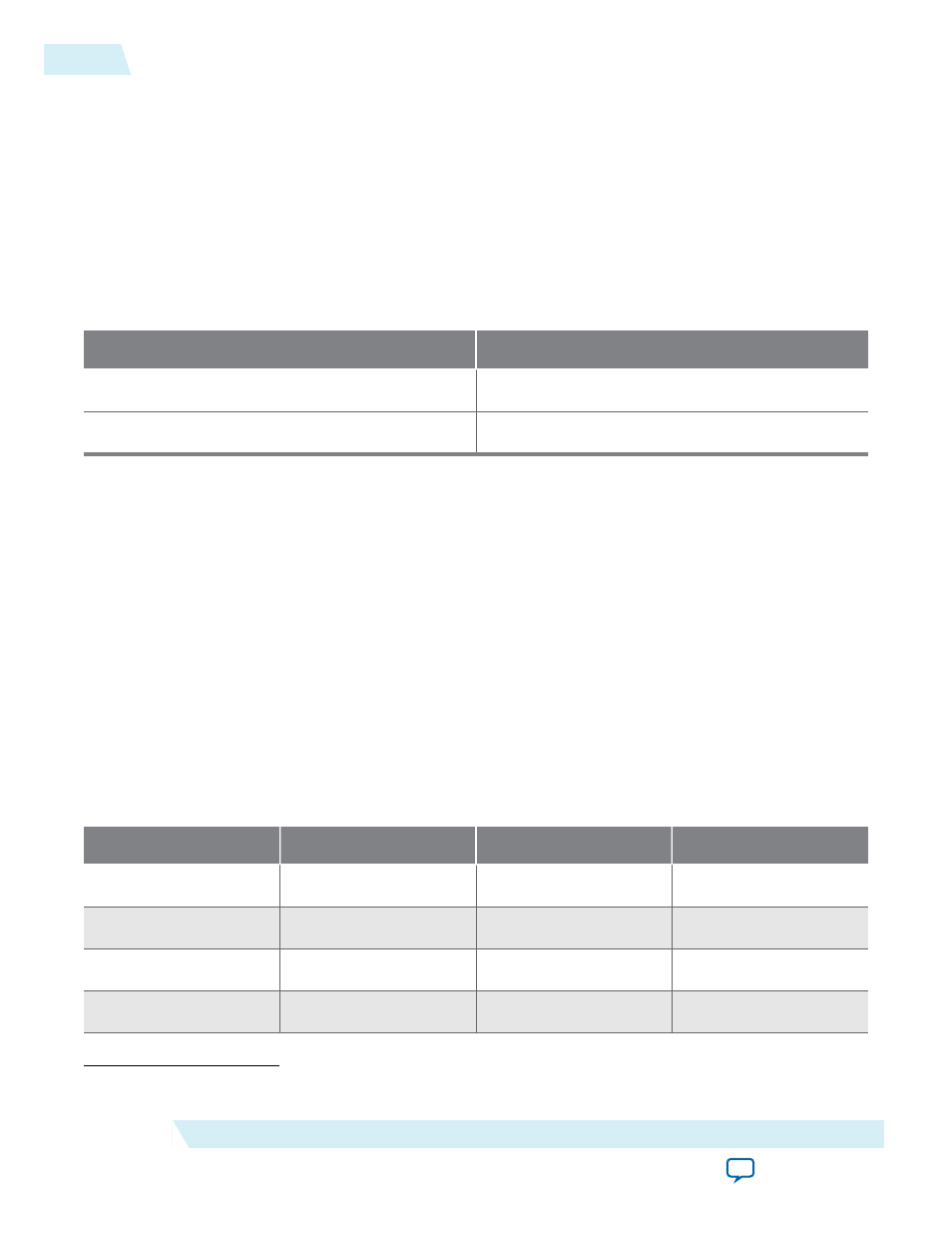

Table 7-2: pclk Clock Frequency

Data Rate

Frequency

Gen1

250 MHz

Gen2

500 MHz

The CDC module implements the asynchronous clock domain crossing between the PHY/MAC

pclk

domain and the Data Link Layer

coreclk

domain. The transceiver

pclk

clock is connected directly to the

Hard IP for PCI Express and does not connect to the FPGA fabric.

Related Information

coreclkout_hip

Table 7-3: Application Layer Clock Frequency for All Combinations of Link Width, Data Rate and

Application Layer Interface Widths

The

coreclkout_hip

signal is derived from

pclk

. The following table lists frequencies for

coreclkout_hip

,

which are a function of the link width, data rate, and the width of the Application Layer to Transaction Layer

interface. The frequencies and widths specified in this table are maintained throughout operation. If the link

downtrains to a lesser link width or changes to a different maximum link rate, it maintains the frequencies it was

originally configured for as specified in this table. (The Hard IP throttles the interface to achieve a lower

throughput.)

Link Width

Maximum Link Rate

Avalon Interface Width

coreclkout_hip

×1

Gen1

64

62.5 MHz

(4)

×1

Gen1

64

125 MHz

×2

Gen1

64

125 MHz

×4

Gen1

64

125 MHz

(4)

This mode saves power

7-6

pclk

UG-01127_avst

2014.12.15

Altera Corporation

Reset and Clocks