Altera SDI II MegaCore User Manual

Page 89

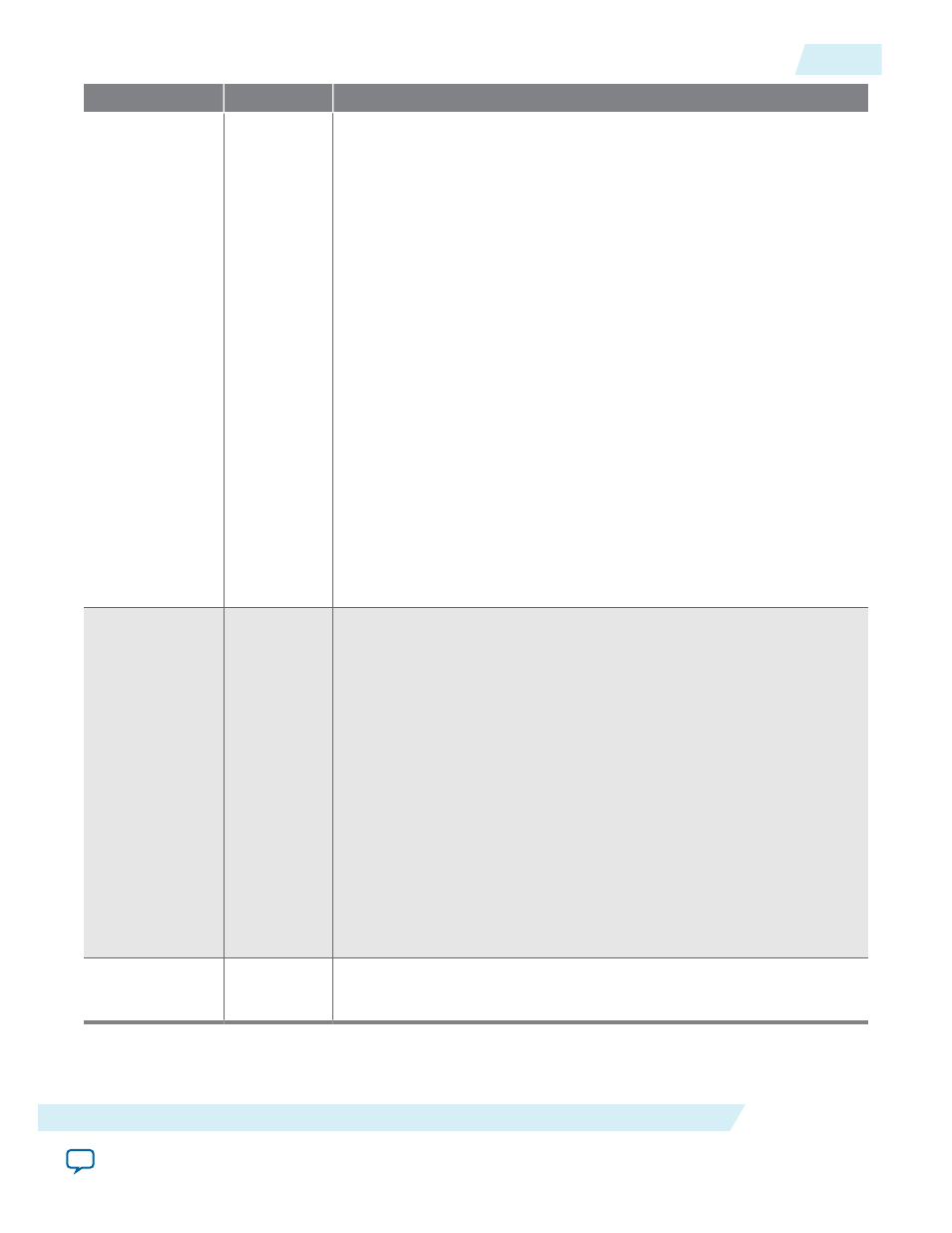

Date

Version

Changes

August 2014

2014.08.18 • Added support for Arria 10 devices.

• Revised the resource utilization table with information about ALM

needed and primary and secondary logic registers.

• Added information related to Arria 10 devices.

• Added new parameters for Example Design Options.

• Added new transceiver information—for the Arria 10 devices, the

SDI II IP core no longer provides the transceiver, and the TX PLL

is no longer wrapped in the transceiver PHY. You must generate

the transceiver and the TX PLL separately.

• Added new transceiver signals:

rx_ready

,

gxb_ltr

,

gxb_ltd

,

rx_

ready_b

,

gxb_ltr_b

,

gxb_ltd_b

, and

trig_rst_ctrl

.

• Added information for the newly added Arria 10 design example.

• Added design example entity and simulation testbench diagram.

• Added connecting input signals:

rx_manual

and

rx_is_

lockedtodata.

• Added information about transceiver reconfiguration controller—

for Arria 10 designs, the reconfiguration interface is integrated

into the Arria 10 Native PHY instance and TX PLL.

• Added transceiver reconfiguration controller signals.

• Added information about IP catalog and removed information about

MegaWizard Plug-In Manager.

July 2013

2013.06.28 • Added a section for each new feature:

• Tx PLL Dynamic Switching

• SMPTE RP168 Switching

• SD Optional 20-bit Interface for Dual/Triple Standard

• Added information about a new submodule, Convert SD Bits.

• Added information about a new parameter, SD Interface Bit Width.

• Added more information about the design example components—

Reconfiguration Management, Reconfiguration Router, Avalon-MM

Translators.

• Added more information about the design example operation:

• Transceiver Dynamic Reconfiguration

• Expanding to Multiple Channels

• Updated the protocol and transceiver signals table.

• Updated the resource utilization table.

November

2012

2012.11.15 Initial release.

UG-01125

2015.05.04

Document Revision History

A-3

Additional Information

Altera Corporation