Altera SDI II MegaCore User Manual

Page 26

This design generates two transceiver PHY reset controllers—one for TX and one for RX. These reset

controllers are connected to the transceiver to control the reset sequence. The PHY adapter controls the

rx_manual

and

rx_is_lockedtodata

input signals of the reset controller. If you want to bypass the PHY

adapter, you must copy the assignment of these input signals in the

sdi_ii_phy_adapter.v

file to your design.

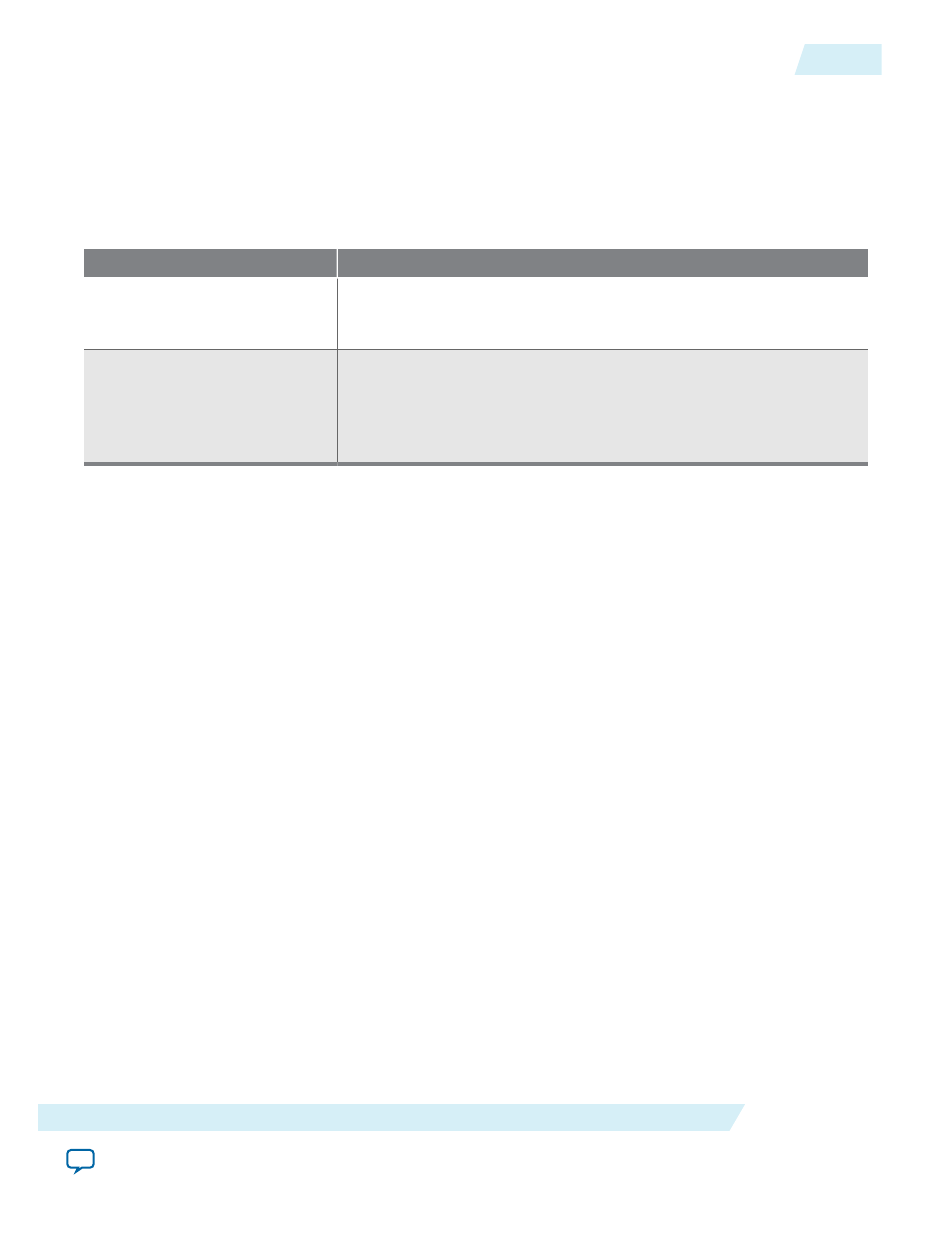

The table below describes how you should connect the input signals.

Table 3-4: Connecting Input Signals

Input Signal

Connection

rx_manual

Connect this signal to the

rx_ready

port of the PHY reset controller to

avoid any disturbance from short interference after the receiver is

locked.

rx_is_lockedtodata

Connect this signal to an output from a multiplexer between

rx_is_

lockedtoref

and

rx_is_lockedtodata

ports from the transceiver,

with the

rx_set_locktoref

acting as the selector. The receiver operates

in

locktoref

mode when it receives SD video data.

rx_is_lockedto-

data

is not stable in this mode.

Note: The Transceiver Reconfiguration Controller that was used in the design examples for Arria V,

Cyclone V, and Stratix V devices are not applicable for Arria 10 devices. The reconfiguration

interface is now integrated into the transceiver. Each transceiver should pair with a reconfiguration

controller if it requires reconfiguration.

Design Examples for Arria V, Cyclone V, and Stratix V Devices

Figure below illustrates the generated design example entity and simulation testbench for Arria V,

Cyclone V, and Stratix V devices. This design example consists of a video pattern generator, transceiver

reconfiguration controller, reconfiguration management, loopback path, and various SDI blocks

occupying two transceiver channels.

UG-01125

2015.05.04

Design Examples for Arria V, Cyclone V, and Stratix V Devices

3-11

SDI II IP Core Getting Started

Altera Corporation