Receiver, Receiver -6, Submodules on page 4-14 – Altera SDI II MegaCore User Manual

Page 48

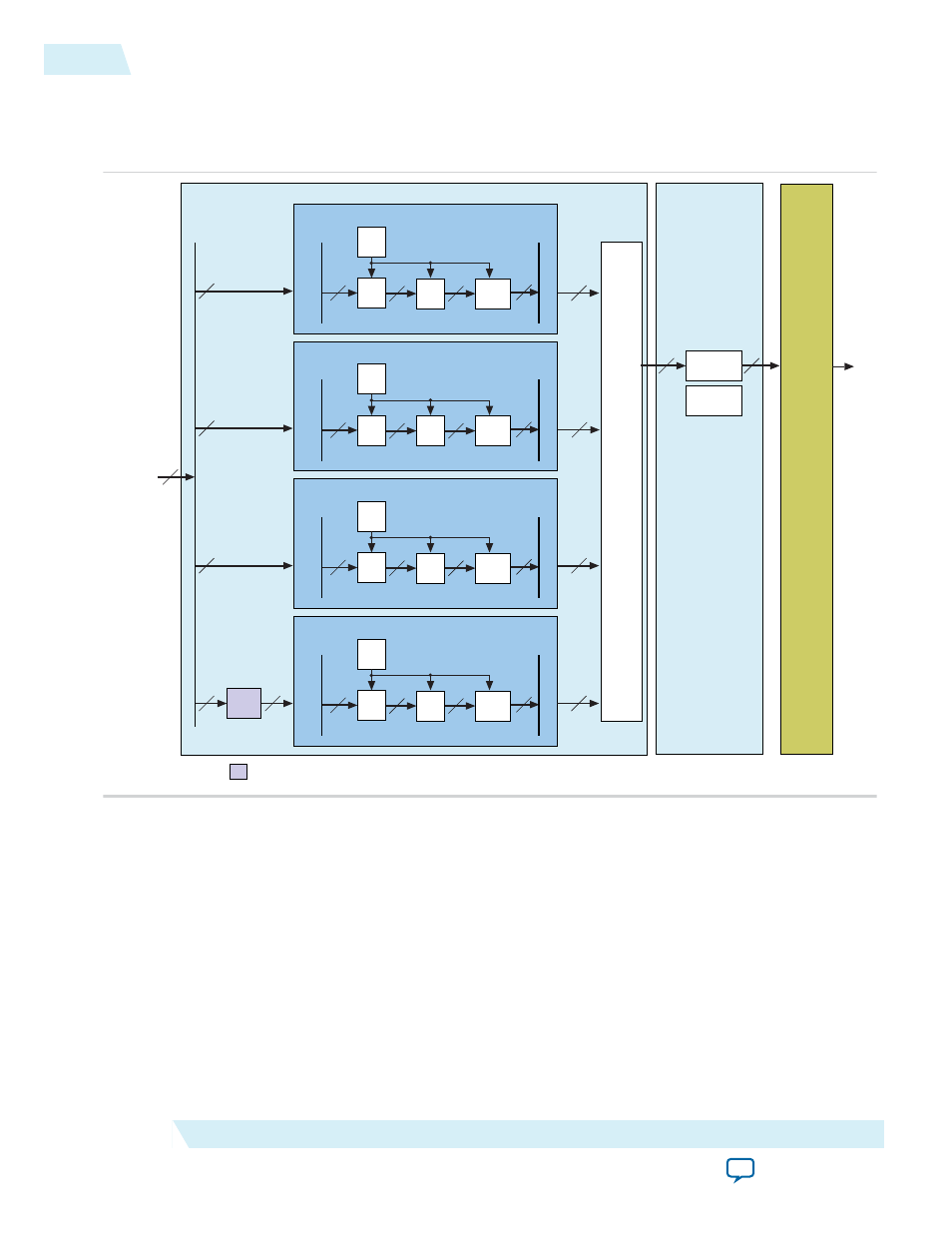

Figure 4-8: Multi Rate (up to 12G-SDI) Transmitter Data Path Block Diagram

Note: The transmit block shown in the diagram is the simplified version of the transmit block in the

Triple Rate SDI Transmitter Data Path Block Diagram.

Scrambler

20

20

80

TX

Oversample

Generate

Clock Enable

TX PHY Management

& PHY Adapter

TX Protocol

80

80

Transceiver

Parallel

Video In

SDI

Out

Convert

SD Bits

Match

TRS

Insert

Line

Multiplexer

Insert

Sync Bits

Transmit

20/40

3 GB

20/40

3 GB

Insert

CRC

20/40

3 GB

Insert

Payload

ID

20/40

3 GB

Demultiplexer

20

Match

TRS

Insert

Line

Multiplexer

Transmit

20/40

3 GB

20/40

3 GB

Insert

CRC

20/40

3 GB

Insert

Payload

ID

20/40

3 GB

Demultiplexer

20

Match

TRS

Insert

Line

Multiplexer

Transmit

20/40

3 GB

20/40

3 GB

Insert

CRC

20/40

3 GB

Insert

Payload

ID

20/40

3 GB

Demultiplexer

20

Match

TRS

Insert

Line

Multiplexer

Transmit

20/40

3 GB

20/40

3 GB

Insert

CRC

20/40

3 GB

Insert

Payload

ID

20/40

3 GB

Demultiplexer

20

20

20

20

For Optional SD 20 bits Only (Not Available for Multi-Rate Mode (up to 12 G) )

Related Information

Receiver

The receiver performs the following functions:

• Video standard detection

• Video rate detection

• NRZI decoding and descrambling

• Word alignment

• Demultiplex data links

• Video timing flags extraction

4-6

Receiver

UG-01125

2015.05.04

Altera Corporation

SDI II IP Core Functional Description