Altera SDI II MegaCore User Manual

Page 71

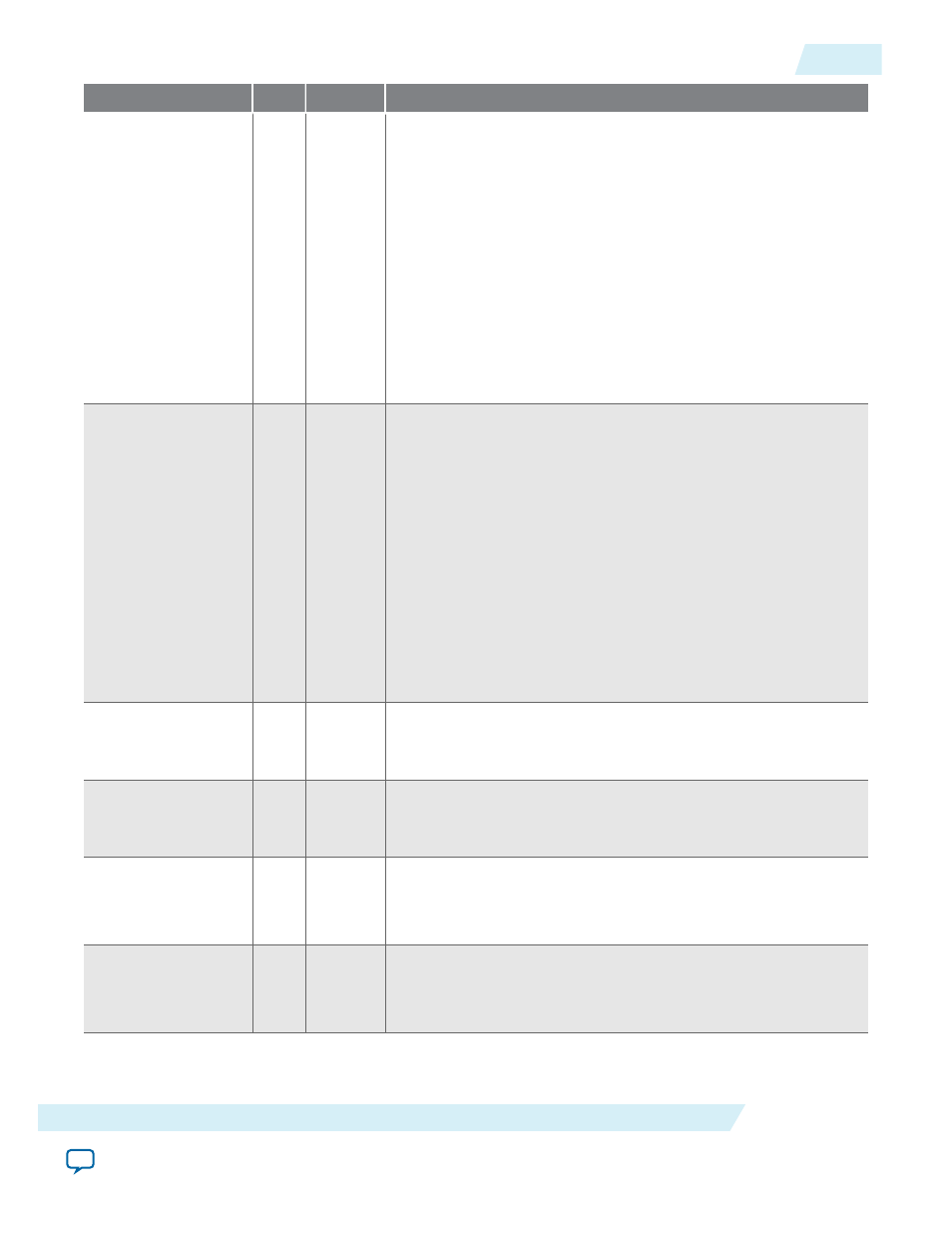

Signal

Width Direction

Description

tx_datain

20S

Input

User-supplied transmitter parallel data.

• SD-SDI = bits 19:10 unused; bits 9:0 C, Y, Cr, Y multiplex

• HD-SDI = bits 19:10 Y; bits 9:0 C

• HD-SDI dual link = bits 19:10 Y link A, bits 9:0 C link A

• 3G-SDI Level A = bits 19:10 Y; bits 9:0 C

• 3G-SDI Level B = bits 19:10 C, Y multiplex (link A); bits 9:0

C, Y multiplex (link B)

• Dual standard = bits 19:10 Y; bits 9:0 C

• Triple standard = bits 19:10 Y; bits 9:0 C

• Multi standard (up to 12G) = bits 79:70 Y of stream 3; bits

69:60 C of stream 3; bits 59:50 Y of stream 2; bits 49:40 C of

stream 2; bits 39:30 Y of stream 1; bits 29:20 C of stream 1;

bits 19:10 Y of stream 0; bits 9:0 C of stream 0

tx_datain_valid

1

Input

Transmitter parallel data valid. The timing (H: High, L: Low)

must be synchronous to

tx_pclk

clock domain and have the

following settings:

• SD-SDI = 1H 4L 1H 5L

• HD-SDI = H

• 3G-SDI = H

• HD-SDI Dual Link = H

• Dual standard = SD (1H 4L 1H 5L); HD (1H 1L)

• Triple standard = SD (1H 4L 1H 5L); HD (1H 1L); 3G (H)

• Multi standard (up to 12G) = SD (1H 4L 1H 5L); HD (1H 1L);

3G/6G/12G (H)

Otherwise, this signal can be driven by the

tx_dataout_valid

signal for SD-SDI, and multi standard modes.

tx_trs

1

Input

Transmitter TRS input. For use in LN, CRC, or payload ID

insertion. Assert this signal on first word of both EAV and SAV

TRSs.

tx_ln_b

11S

Input

Transmitter line number for link B. For use in 3G-SDI, HD-SDI

dual link, triple standard, and multi standard (up to 12G) line

number insertion.

tx_datain_b

20

Input

User-supplied transmitter parallel data for link B. Applicable for

HD-SDI dual link mode only.

• HD-SDI dual link = bits 19:10 Y link B, bits 9:0 C link B

tx_datain_valid_

b

1

Input

Transmitter parallel data valid for link B. Applicable for HD-SDI

dual link mode only.

• HD-SDI dual link = H

UG-01125

2015.05.04

SDI II IP Core Signals

4-29

SDI II IP Core Functional Description

Altera Corporation