Altera SDI II MegaCore User Manual

Page 70

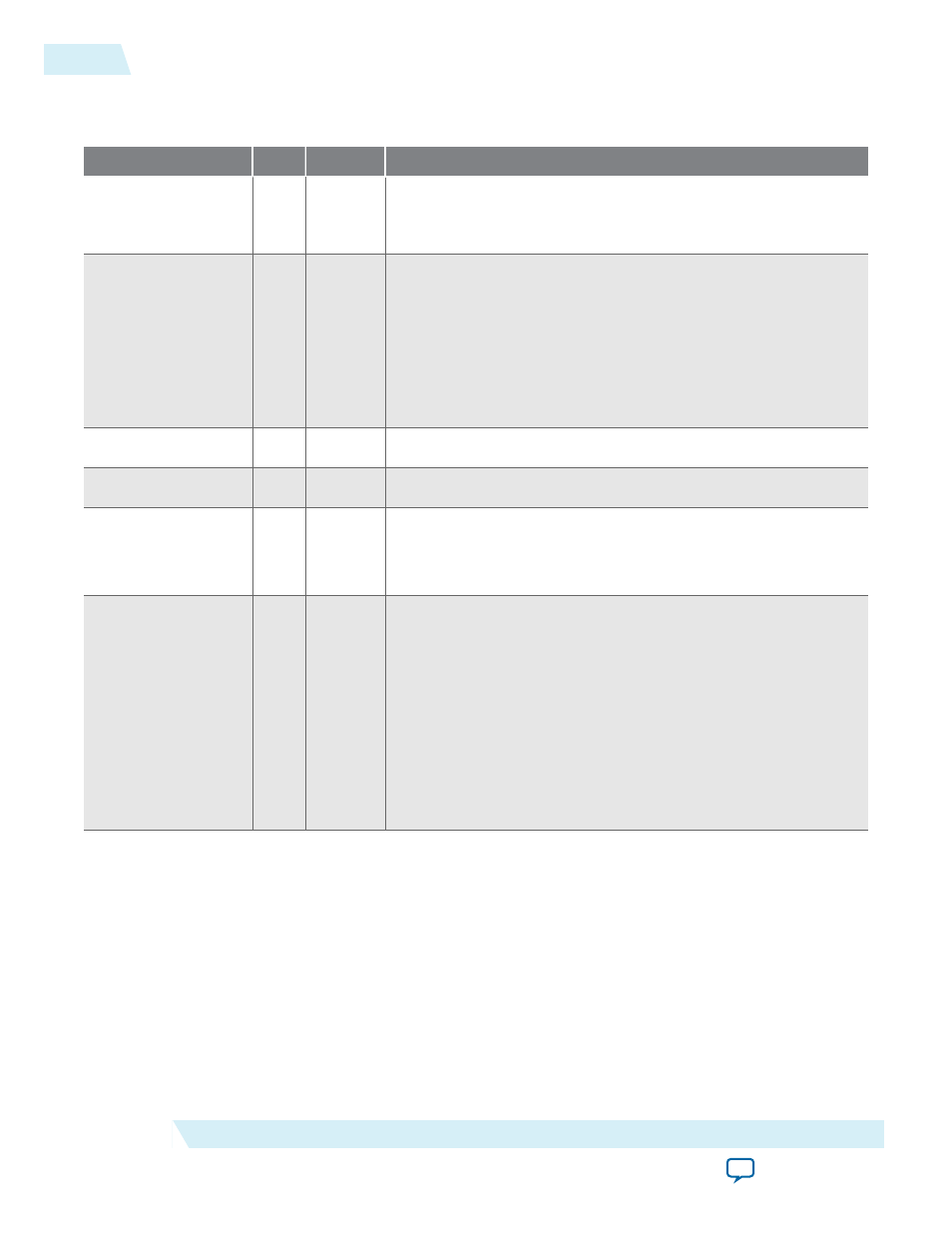

Table 4-5: Transmitter Protocol Signals

Note: S = Indicates the number of streams; 4 for multi standard (up to 12G) mode and 1 for other modes.

Signal

Width Direction

Description

tx_rst

1

Input

Transmitter reset signal. This signal is active high and level

sensitive. This reset signal must be synchronous to

tx_coreclk

clock domain.

tx_pclk

1

Input

Transmitter parallel clock input. Driven by the

tx_clkout

signal.

• SD-SDI = 148.5 MHz

• HD-SDI = 74.25 MHz or 74.175 MHz

• 3G-SDI/6G-SDI/12G-SDI = 148.5 MHz or 148.35 MHz

• HD-SDI Dual Link = 74.25 MHz or 74.175 MHz

• Dual Standard = 148.5 MHz or 148.35 MHz

• Triple Standard = 148.5 MHz or 148.35 MHz

tx_enable_crc

1

Input

Enables CRC insertion for all modes except SD-SDI.

tx_enable_ln

1

Input

Enables LN insertion for all modes except SD-SDI.

tx_ln

11S

Input

Transmitter line number.

Not applicable when you disable the Insert Video Payload ID

(SMPTE 352M) option in SD-SDI.

tx_std

2

Input

Transmitter video standard. Applicable for 3G-SDI and multi

standard only.

• SD-SDI = 000

• HD-SDI = 001

• 3G-SDI Level B = 010

• 3G-SDI Level A = 011

• 6G-SDI Level B = 100

• 6G-SDI Level A = 101

• 12G-SDI Level B = 110

• 12G-SDI Level A = 111

4-28

SDI II IP Core Signals

UG-01125

2015.05.04

Altera Corporation

SDI II IP Core Functional Description