Altera SDI II MegaCore User Manual

Page 85

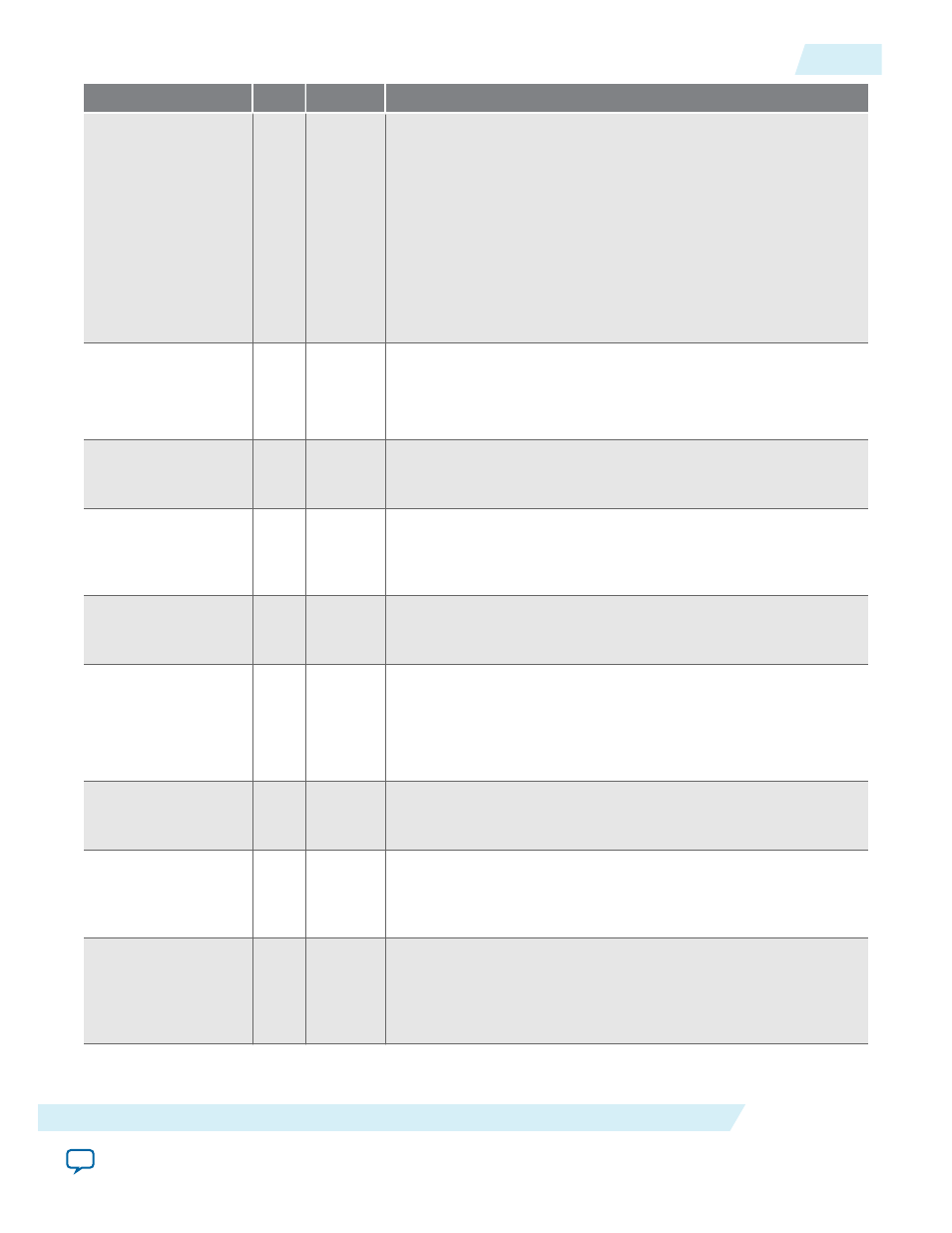

Signal

Width Direction

Description

tx_dataout_valid

1

Output

Data valid generated by the core. This signal can be used to drive

tx_datain_valid

. The timing (H: High, L: Low) must be

synchronous to

tx_pclk

clock domain and have the following

settings:

• SD-SDI = 1H 4L 1H 5L

• HD-SDI = H

• 3G-SDI = H

• HD-SDI Dual Link = H

• Dual Standard = SD (1H 4L 1H 5L); HD (1H 1L)

• Triple Standard = SD (1H 4L 1H 5L); HD (1H 1L); 3G (H)

tx_dataout_

valid_b

1

Output

Data valid generated by the core for link B. For HD-SDI dual link

mode only. The timing (H: High, L: Low) is identical to the

tx_

dataout_valid

signal and is synchronous to

tx_pclk

clock

domain.

sdi_tx

1

Output

Serial output signal for the hard transceiver.

Note: Not applicable for Arria 10 devices.

sdi_tx_b

1

Output

Serial output signal for the hard transceiver (link B). Applicable

for HD-SDI dual link configuration only.

Note: Not applicable for Arria 10 devices.

tx_pll_locked

1

Output

PLL locked signal (TX PLL0) for the hard transceiver.

Note: Not applicable for Arria 10 devices.

tx_pll_locked_

alt

1

Output

PLL locked signal (TX PLL1) for the hard transceiver.

Applicable only when you enable the TX PLL Dynamic

Switching option.

Note: Not applicable for Arria 10 devices.

tx_clkout

1

Output

PLL clock output signal for the hard transceiver.

Note: Not applicable for Arria 10 devices.

rx_ready

1

Input

Status signal from the transceiver reset controller to indicate

when Rx PHY sequence is complete.

Note: Applicable only for Arria 10 devices.

rx_ready_b

1

Input

Status signal from the transceiver reset controller to indicate

when Rx PHY sequence is complete (link B). Applicable for HD-

SDI dual link receiver protocol configuration only.

Note: Applicable only for Arria 10 devices.

UG-01125

2015.05.04

SDI II IP Core Signals

4-43

SDI II IP Core Functional Description

Altera Corporation