Altera SDI II MegaCore User Manual

Page 39

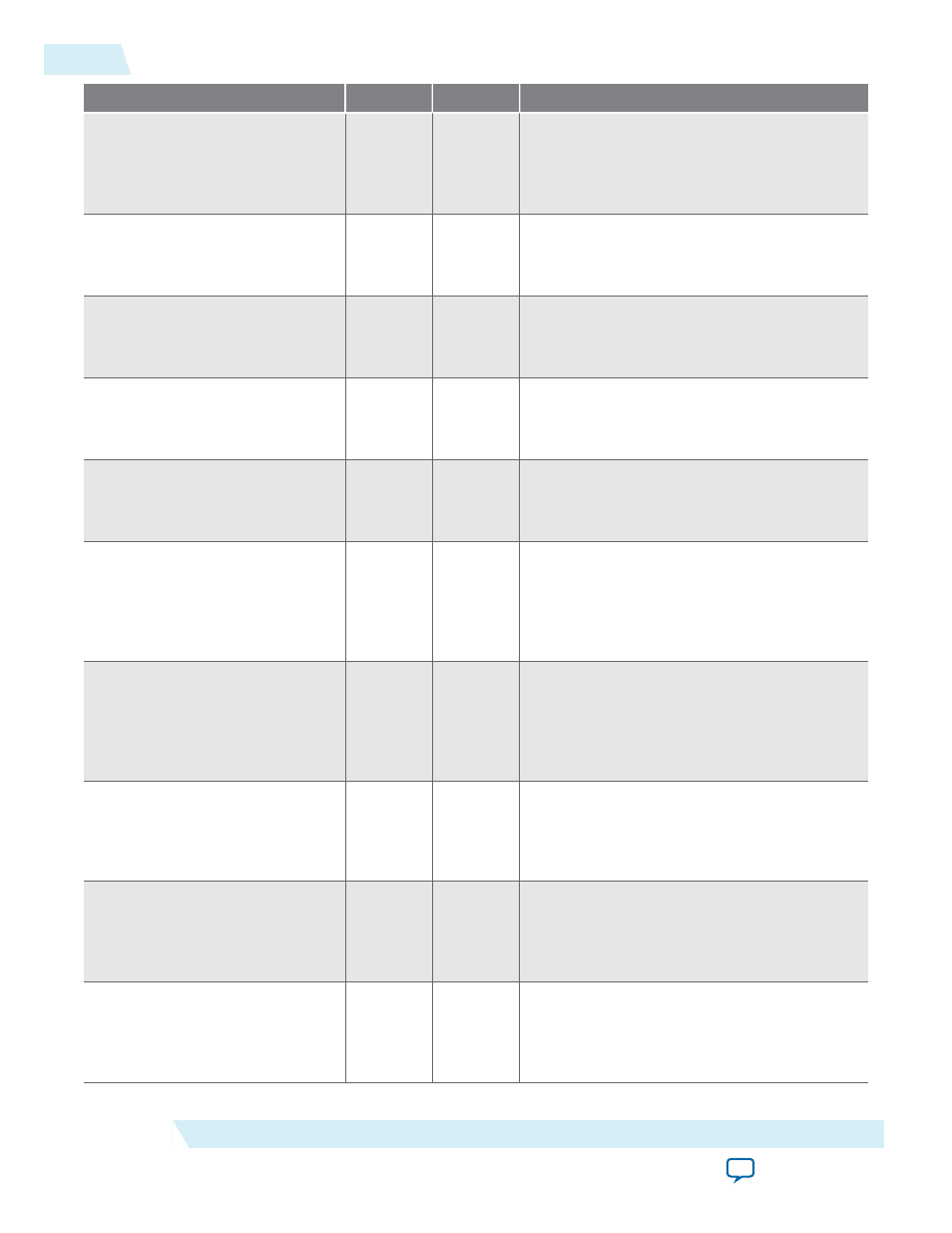

Signal

Width

Direction

Description

xcvr_reconfig_rst

1

Input

Reset signal for reconfiguration user logic.

This signal is active high and level sensitive.

This reset signal must share the same reset

source as

reconfig_reset

in the transceiver.

xcvr_reconfig_write

1

Output

Write enable signal.

Connect this signal to

reconfig_write

in the

transceiver.

xcvr_reconfig_read

1

Output

Read enable signal.

Connect this signal to

reconfig_read

in the

transceiver.

xcvr_reconfig_address

10

Output

Reconfiguration address.

Connect this signal to

reconfig_address

in

the transceiver.

xcvr_reconfig_writedata

32

Output

A 32-bit data write bus.

Connect this bus to

reconfig_writedata

in

the transceiver.

xcvr_reconfig_readdata

32

Input

A 32-bit data read bus. This signal returns

valid data from the transceiver after a read

operation.

Connect this bus to

reconfig_readdata

in

the transceiver.

xcvr_reconfig_waitrequest

1

Input

Status signal from the transceiver that

indicates that the Avalon-MM interface is

busy.

Connect this signal to

reconfig_

waitrequest

in the transceiver.

cdr_reconfig_sel

2

Input

Signal to specify which data rate the CDR

should be configured to.

Connect this signal to

rx_std

in the SDI II

IP core.

cdr_reconfig_req

1

Input

Request signal to start the CDR dynamic

reconfiguration.

Connect this signal to

rx_sdi_start_

reconfig

in the SDI II IP core.

cdr_reconfig_busy

1

Output

Status signal that indicates that CDR reconfi‐

guration is taking place.

Connect this signal to

rx_sdi_reconfig_

done

in the SDI II IP core.

3-24

Transceiver Reconfiguration Controller Signals

UG-01125

2015.05.04

Altera Corporation

SDI II IP Core Getting Started