Altera SDI II MegaCore User Manual

Page 84

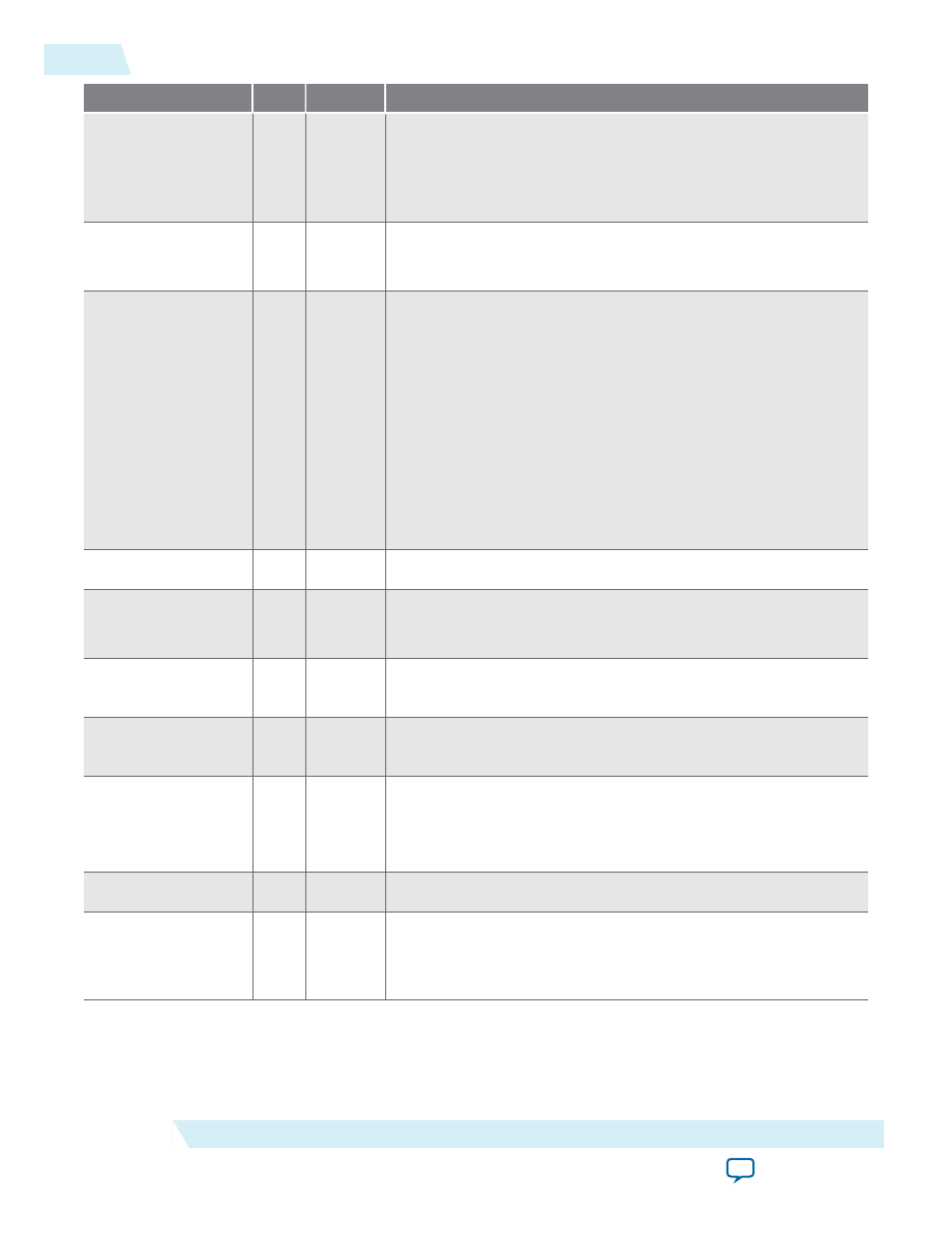

Signal

Width Direction

Description

rx_clkout_is_

ntsc_paln

1

Input

Indicates the video rate received. Applicable for all modes except

SD-SDI.

• 0 = PAL rate

• 1 = NTSC rate

rx_dataout

20

Output

Parallel data out signal for the receiver.

Note: Not applicable for Arria 10 devices.

rx_dataout_valid

1

Output

Data valid from the oversampling logic. The receiver asserts this

signal to indicate current data on

rx_dataout

is valid. The

timing (H: High, L: Low) for each video standard must have the

following settings:

• SD-SDI = 1H 4L 1H 5L

• HD-SDI = H

• 3G-SDI = H

• HD-SDI Dual Link = H

• Dual standard = SD (1H 4L 1H 5L); HD (H)

• Triple standard = SD (1H 4L 1H 5L); HD (H); 3G (H)

Note: Not applicable for Arria 10 devices.

rx_clkout

1

Output

CDR clock output signal for the hard transceiver.

rx_pll_locked

1

Output

CDR PLL locked signal for the hard transceiver.

Note: Not applicable for Arria 10 devices.

rx_rst_proto_

out_b

1

Output

Reset the receiver protocol downstream logic. Applicable for HD-

SDI dual link configuration only.

rx_dataout_b

20

Output

Parallel data out signal for the receiver (link B). Applicable for

HD-SDI dual link configuration only.

rx_dataout_

valid_b

1

Output

Data valid from the oversampling logic. The receiver asserts this

signal to indicate current data on

rx_dataout_b

is valid. The

timing (H: High, L: Low) for each video standard is identical to

the

rx_dataout_valid

signal.

rx_clkout_b

1

Output

CDR clock output signal for the hard transceiver (link B).

rx_pll_locked_b

1

Output

CDR PLL locked signal for the hard transceiver (link B).

Applicable for HD-SDI dual link configuration only.

Note: Not applicable for Arria 10 devices.

4-42

SDI II IP Core Signals

UG-01125

2015.05.04

Altera Corporation

SDI II IP Core Functional Description