Rx sample, Rx sample -19 – Altera SDI II MegaCore User Manual

Page 61

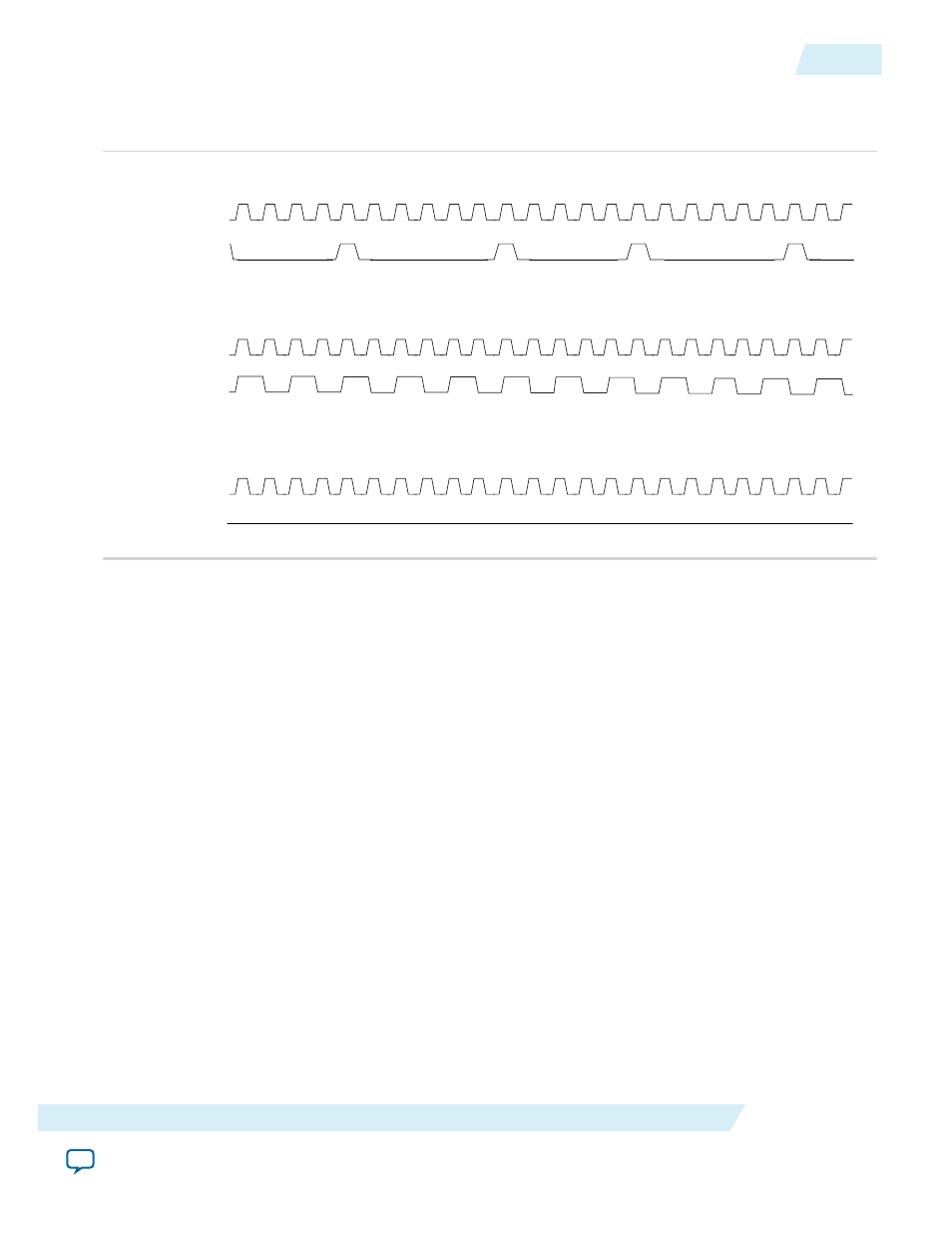

Figure 4-20: Triple Rate Transmit Clocking Scheme

Figure below illustrates the behavior of the

tx_datain_valid

pulse in each video standard.

tx_pclk

(148.5 @ 148.35 MHz)

SD-SDI

tx_datain_valid

tx_datain_valid

tx_datain_valid

5

11

5

11

tx_pclk

(148.5 @ 148.35 MHz)

HD-SDI

5

11

5

11

tx_pclk

(148.5 @ 148.35 MHz)

3G-SDI/6G-SDI/12G-SDI

5

11

5

11

RX Sample

This submodule extracts data from the oversampled incoming data stream. In oversampling schemes,

each bit is repeated many times. For example, a stream of 0 1 0 1 may look like 000111000111 at the

oversample clock or data rate.

This submodule examines the incoming data stream for logic transitions. These transitions mark the

boundaries of the incoming data bit. It is desirable to extract a sample at a point between these two

boundaries. This submodule identifies a transition, then extracts the sample X clocks after this transition.

When no transitions are present in the incoming data stream, the submodule uses knowledge of oversam‐

pling rate to continuously sample the incoming data at a particular rate. When the next transition is

present, the scheme resets and the sampling aligns to this new transition.

UG-01125

2015.05.04

RX Sample

4-19

SDI II IP Core Functional Description

Altera Corporation