Altera SDI II MegaCore User Manual

Page 5

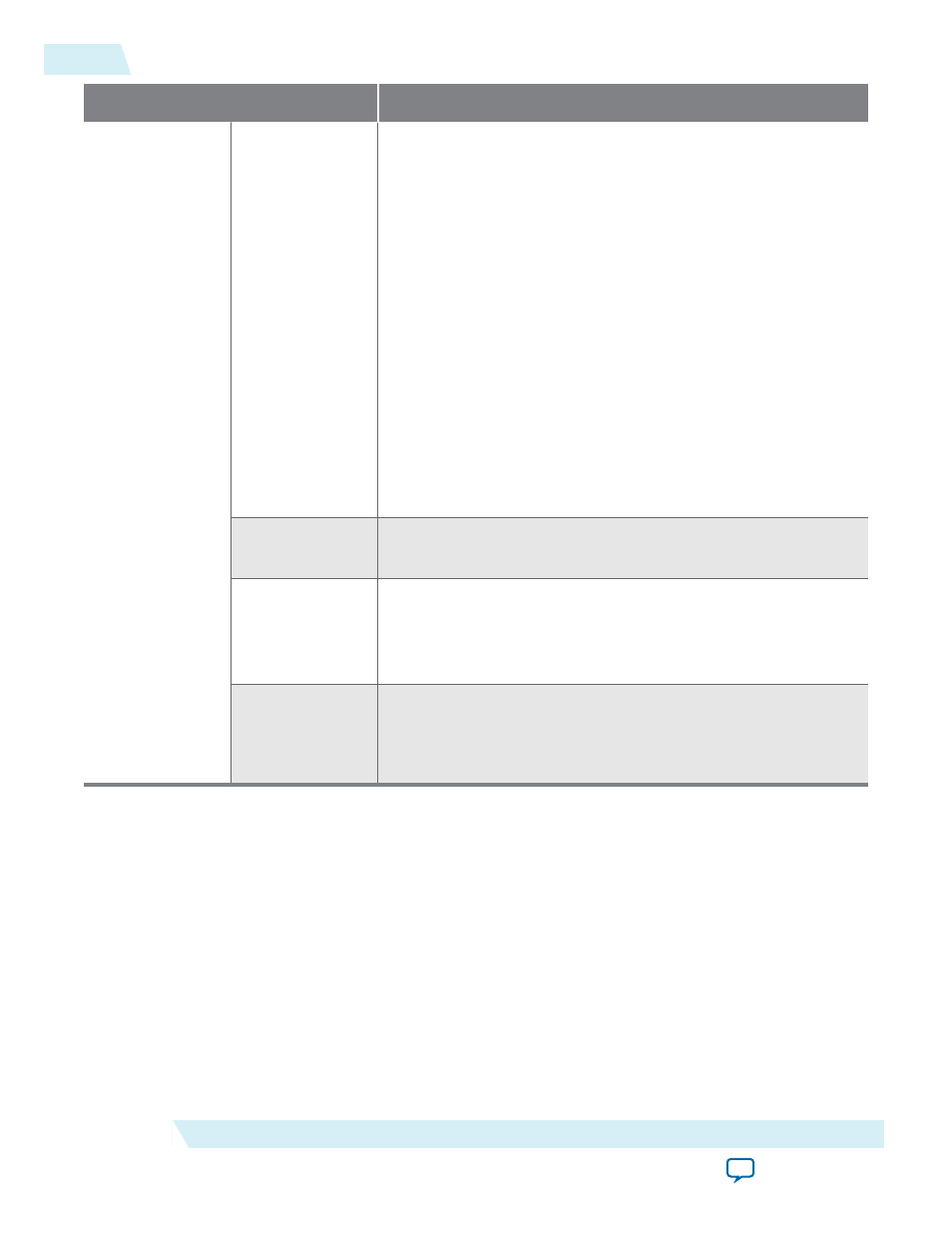

Item

Description

Features

• 20-bit interface support for SD-SDI

• Multiple SDI standards and video formats

• Payload identification packet insertion and extraction

• Clock enable generator

• Video rate detection

• Cyclical redundancy check (CRC) encoding and decoding

(except SD)

• Line number (LN) insertion and extraction (except SD)

• Word scrambling and descrambling

• Word alignment

• Framing and extraction of video timing signals

• Dual link data stream synchronization (except SD)

• Transceiver dynamic reconfiguration

• RP168 support for synchronous video switching

• Dynamic TX clock switching

• OpenCore Plus evaluation

• SMPTE425M level A support (direct source image formatting)

• SMPTE425M level B support (dual link mapping)

Application

• Digital video equipment

• Mixing and recording equipment

Device Family

Support

Arria

®

10 (preliminary), Arria V GX, Arria V GZ, Cyclone

®

V,

and Stratix

®

V FPGA device families.

Refer to the device support table and What’s New in Altera page of

the Altera website for detailed information.

Design Tools

• IP Catalog in the Quartus II software for design creation and

compilation

• ModelSim

®

-Altera, Riviera-Pro, and VCS/VCS MX software

for design simulation or synthesis

Related Information

•

•

1-2

SDI II IP Core Quick Reference

UG-01125

2015.05.04

Altera Corporation

SDI II IP Core Quick Reference