Altera SDI II MegaCore User Manual

Page 81

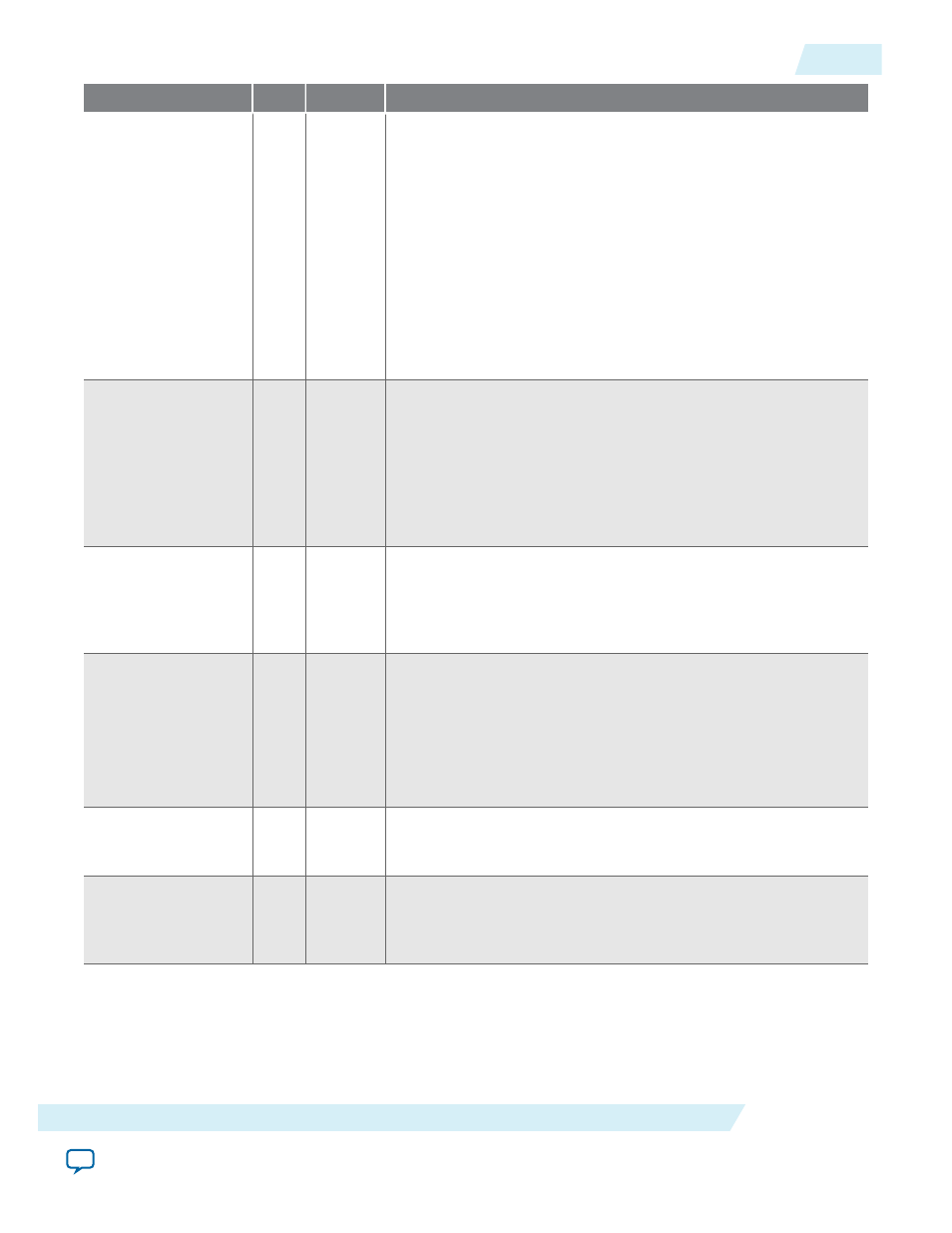

Signal

Width Direction

Description

xcvr_refclk_alt

1

Input

Alternative clock input for the hard transceiver. The frequency of

this signal must be the alternate frequency value of the

xcvr_

refclk

signal.

• HD-SDI = 74.25 MHz or 74.175 MHz

• 3G-SDI = 148.5 MHz or 148.35 MHz

• HD-SDI Dual Link: 74.25 MHz or 74.175 MHz

• Dual Standard: 148.5 MHz or 148.35 MHz

• Triple Standard: 148.5 MHz or 148.35 MHz

Applicable only when you enable the Tx PLL Dynamic

Switching option.

Note: Not applicable for Arria 10 devices.

xcvr_refclk_sel

1

Input

TX PLL select signal for the transceiver reset controller.

• 0 = Lock TX PLL using TX PLL0

• 1 = Lock TX PLL using TX PLL1

Applicable only when you enable the TX PLL Dynamic

Switching option.

Note: Not applicable for Arria 10 devices.

rx_trs_loose_

lock_in

1

Input

Indicates that the receiver protocol block detects a single and

valid TRS locking signal. This signal must be driven by

rx_trs_

loose_lock_out

of the receiver protocol block.

Note: Not applicable for Arria 10 devices.

rx_trs_loose_

lock_in_b

1

Input

Indicates that the receiver protocol block for link B detects a

single and valid TRS locking signal. This signal must be driven by

rx_trs_loose_lock_out_b

of the receiver protocol block.

Applicable for HD-SDI dual link receiver transceiver configura‐

tion only.

Note: Not applicable for Arria 10 devices.

sdi_rx

1

Input

Serial input signal for the hard transceiver.

Note: Not applicable for Arria 10 devices.

sdi_rx_b

1

Input

Serial input signal for the hard transceiver (link B). Applicable

for HD-SDI dual link configuration only.

Note: Not applicable for Arria 10 devices.

UG-01125

2015.05.04

SDI II IP Core Signals

4-39

SDI II IP Core Functional Description

Altera Corporation