Clocking scheme, Sdi ii ip core signals, Clocking scheme -27 – Altera SDI II MegaCore User Manual

Page 69: Sdi ii ip core signals -27

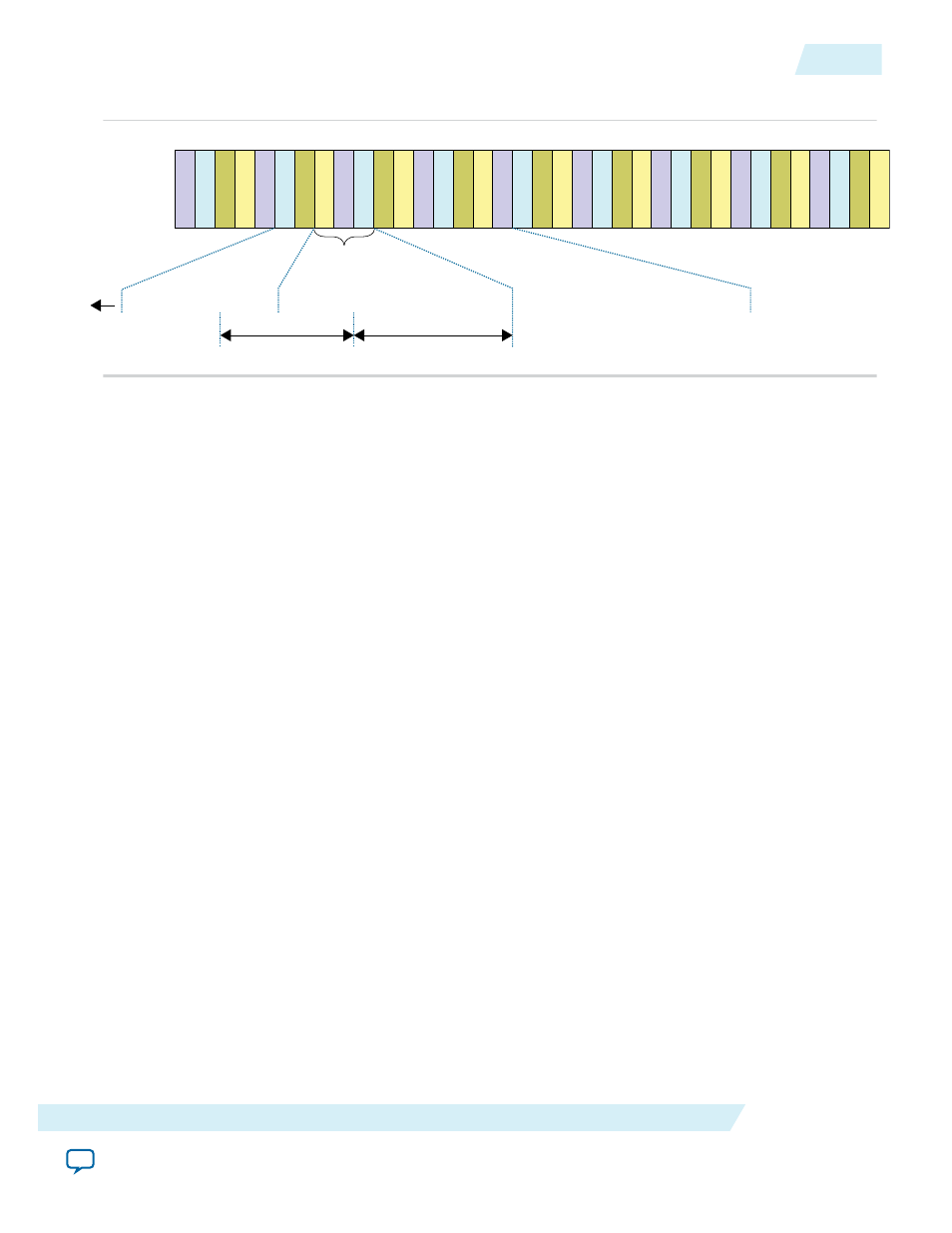

Figure 4-23: Sync Bits Insertion Process

EA

V 3FD (

C)

EA

V 3FD (

C)

EA

V 3FD (

C)

EA

V 3FD (

C)

EA

V 3FD (

Y)

EA

V 3FD (

Y)

EA

V 3FD (

Y)

EA

V 3FF (

Y)

EA

V 000 (

C)

EA

V 000 (

C)

EA

V 002 (

C)

EA

V 002 (

C)

EA

V 002 (

Y)

EA

V 002 (

Y)

EA

V 002 (

Y)

EA

V 002 (

Y)

EA

V 002 (

C)

EA

V 002 (

C)

EA

V 002 (

C)

EA

V 002 (

C)

EA

V 002 (

Y)

EA

V 002 (

Y)

EA

V 002 (

Y)

EA

V 002 (

Y)

EA

V X

YZ (

C)

EA

V X

YZ (

C)

EA

V X

YZ (

C)

EA

V X

YZ (

C)

EA

V X

YZ (

Y)

EA

V X

YZ (

Y)

EA

V X

YZ (

Y)

EA

V X

YZ (

Y)

LN0 (

C)

LN0 (

C)

LN0 (

C)

LN0 (

C)

10-bit Multiplex after Sync Bit Insertion

1011111111 1011111111 1111111111 0000000000 0000000000 0100000000 0100000000 0100000000

LSB

MSB

18 “1”s

20 “0”s

Worst-Case Run of “1”s

Worst-Case Run of “0”s

3FF, 000, 000 Sequence

Left Intact for Framing

Similar to other submodules, assert the

tx_trs

signal for the first word of both EAV and SAV TRS for

correct bit insertion.

This sync bit insertion process is reversed in the receiver. It restores the original 3FFh and 000h data

patterns.

Clocking Scheme

To reduce design complexity and logic resource utilization, the SDI II IP core implements a clock enable

generator submodule to replace both the PLL at the parallel clock domain and the FIFO buffer in the

transceiver interface block.

For the oversampling rate, the SDI II IP core clocking scheme is standardized by applying an oversam‐

pling rate of 11 times for SD-SDI, dual, and triple rate modes.

Related Information

on page 4-18

The clock enable generator is a simple logic that generates a clock enable signal.

SDI II IP Core Signals

The following tables list the SDI II IP core signals by components.

• Protocol blocks—transmitter, receiver

• Transceiver blocks—PHY management, PHY adapter, hard transceiver

Note: These signals are applicable for Arria 10, Arria V, Cyclone V, and Stratix V devices unless specified

otherwise.

UG-01125

2015.05.04

Clocking Scheme

4-27

SDI II IP Core Functional Description

Altera Corporation