Altera SDI II MegaCore User Manual

Page 82

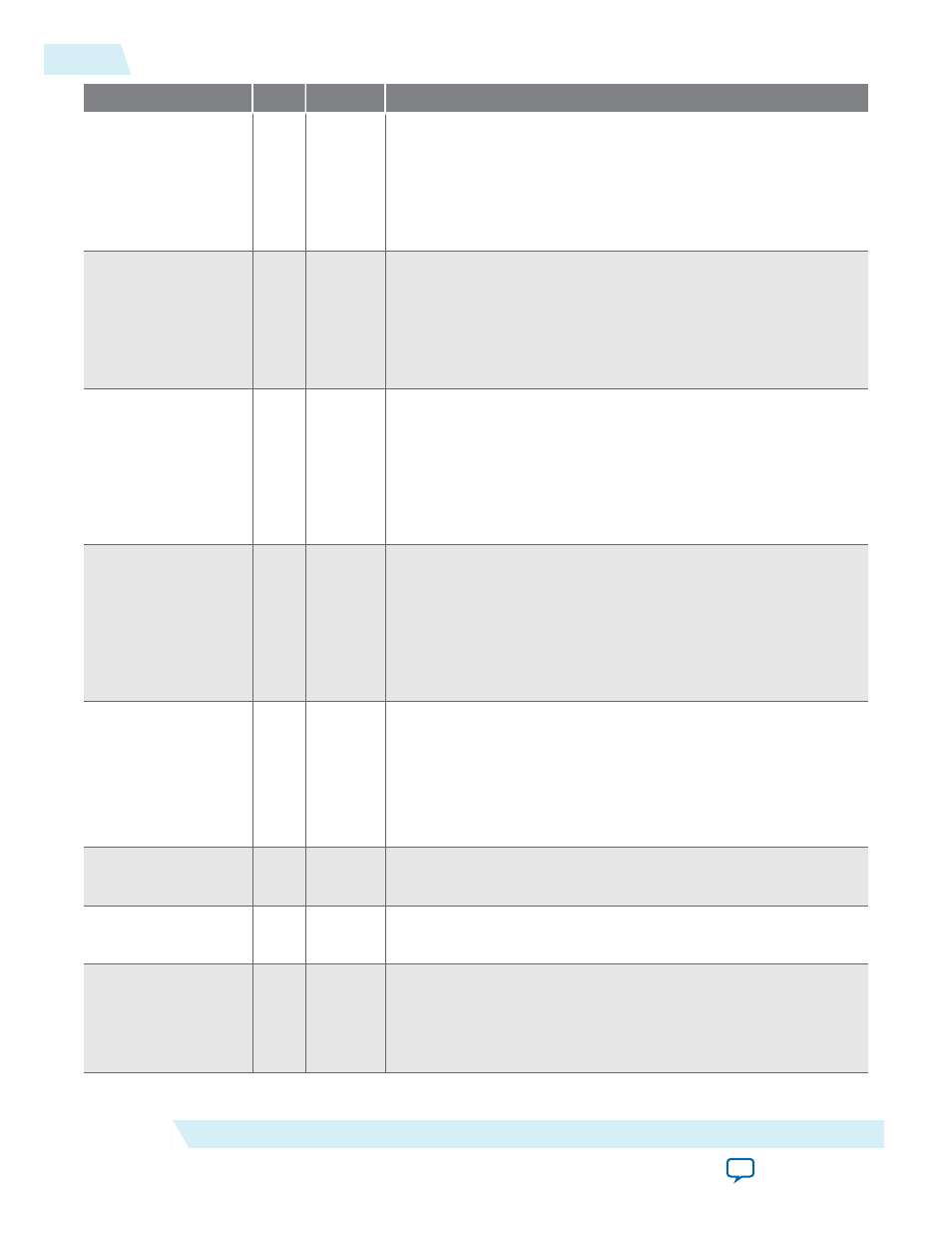

Signal

Width Direction

Description

reconfig_to_xcvr

70N

Input

Dynamic reconfiguration input for the hard transceiver, where N

is the reconfiguration interface.

• N = 1 for receiver

• N = 2 for transmitter and bidirectional

Note: Not applicable for Arria 10 devices.

reconfig_from_

xcvr

46N

Output

Dynamic reconfiguration output for the hard transceiver, where

N is the reconfiguration interface.

• N = 1 for receiver

• N = 2 for transmitter and bidirectional

Note: Not applicable for Arria 10 devices.

reconfig_to_

xcvr_b

70N

Input

Dynamic reconfiguration input for the hard transceiver (link B),

where N is the reconfiguration interface. For HD-SDI dual link

configuration only.

• N = 1 for receiver

• N = 2 for transmitter and bidirectional

Note: Not applicable for Arria 10 devices.

reconfig_from_

xcvr_b

46N

Output

Dynamic reconfiguration output for the hard transceiver (link B),

where N is the reconfiguration interface. For HD-SDI dual link

configuration only.

• N = 1 for receiver

• N = 2 for transmitter and bidirectional

Note: Not applicable for Arria 10 devices.

rx_coreclk_is_

ntsc_paln

1

Input

Indicates the incoming video rate. For use in all modes except

SD-SDI.

• 0 = PAL rate (when

rx_coreclk

= 148.5 MHz or

rx_

coreclk_hd

= 74.25 MHz)

• 1 = NTSC rate (when

rx_coreclk

= 148.35 MHz or

rx_

coreclk_hd

= 74.175 MHz)

rx_sdi_start_

reconfig

1

Output

Request to start dynamic reconfiguration. Applicable for dual

standard and triple standard modes only.

rx_sdi_reconfig_

done

1

Input

Indicates that dynamic reconfiguration has completed.

Applicable for dual standard and triple standard modes only.

rx_clkin_

smpte372

1

Input

Clock input for level A to level B and level B to level A

operations.

• Level A to level B = 148.5 MHz or 148.35 MHz

• Level B to level A = 74.25 MHz or 74.175 MHz

4-40

SDI II IP Core Signals

UG-01125

2015.05.04

Altera Corporation

SDI II IP Core Functional Description