Vhdl component declaration, Ports, Vhdl component declaration -3 – Altera Integer Arithmetic IP User Manual

Page 76: Ports -3

input wire sclr,

input wire [width_s-1:0] sel,

input wire sload_coeff,

input wire sload_data)/* synthesis syn_black_box=1 */;

endmodule

VHDL Component Declaration

The VHDL component declaration is located in the VHDL Design File (.vhd)

altera_mf_components.vhd in the

\libraries\vhdl\altera_mf

directory.

component altmemmult

generic (

coeff_representation:string := "SIGNED";

coefficient0:string := "UNUSED";

data_representation:string := "SIGNED";

intended_device_family:string := "unused";

max_clock_cycles_per_result:natural := 1;

number_of_coefficients:natural := 1;

ram_block_type:string := "AUTO";

total_latency:natural;

width_c:natural;

width_d:natural;

width_r:natural;

width_s:natural := 1;

lpm_hint:string := "UNUSED";

lpm_type:string := "altmemmult");

port(

clock:in std_logic;

coeff_in:in std_logic_vector(width_c-1 downto 0) := (others => '0');

data_in:in std_logic_vector(width_d-1 downto 0);

load_done:out std_logic;

result:out std_logic_vector(width_r-1 downto 0);

result_valid:out std_logic;

sclr:in std_logic := '0';

sel:in std_logic_vector(width_s-1 downto 0) := (others => '0');

sload_coeff:in std_logic := '0';

sload_data:in std_logic := '0');

end component;

Ports

The following tables list the input and output ports for the ALTMEMMULT megafunction.

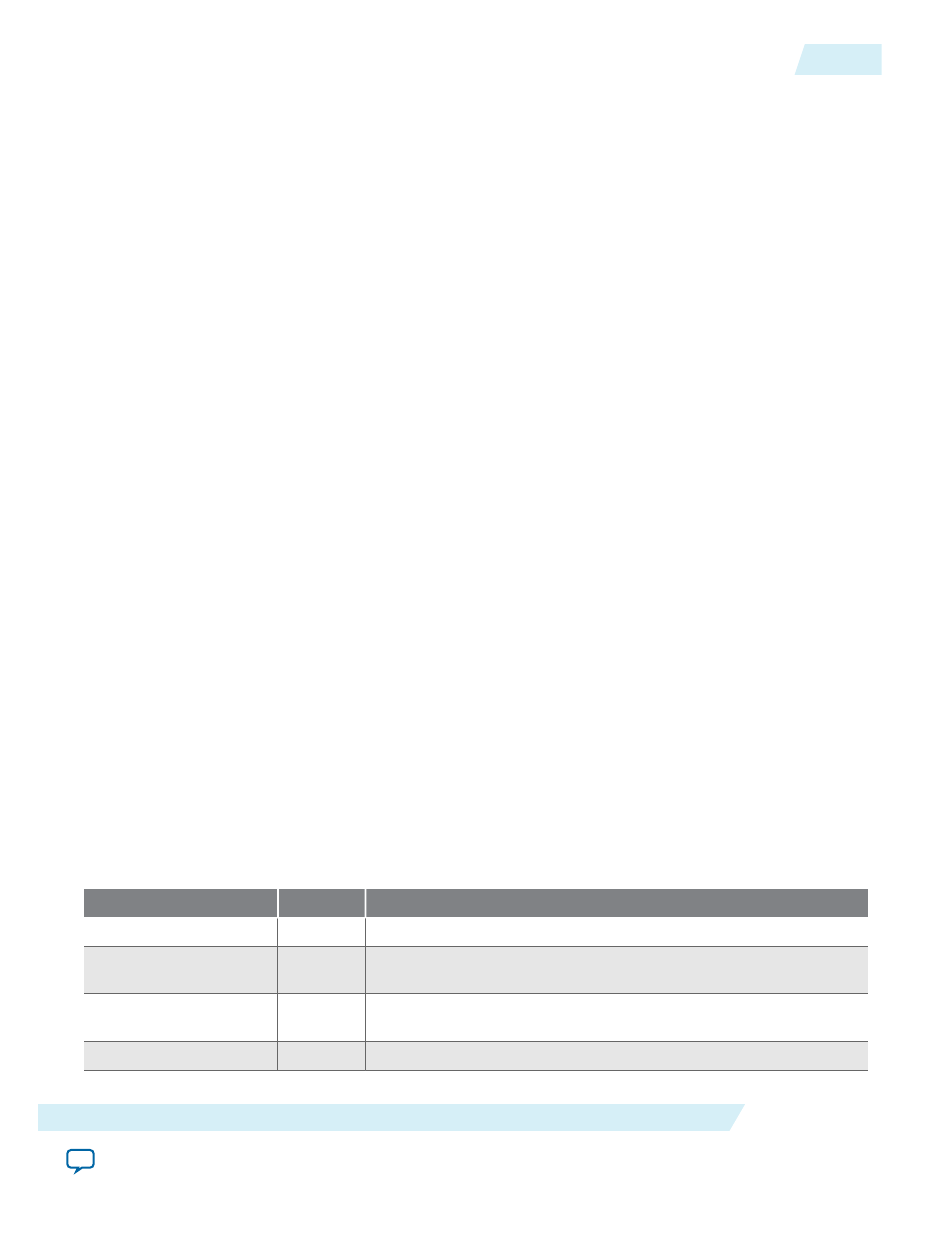

Table 7-2: ALTMEMMULT Megafunction Input Ports

Port Name

Required

Description

clock

Yes

Clock input to the multiplier.

coeff_in[]

No

Coefficient input port for the multiplier. The size of the input port

depends on the

WIDTH_C

parameter value.

data_in[]

Yes

Data input port to the multiplier. The size of the input port depends

on the

WIDTH_D

parameter value.

sclr

No

Synchronous clear input. If unused, the default value is active high.

UG-01063

2014.12.19

VHDL Component Declaration

7-3

ALTMEMMULT (Memory-based Constant Coefficient Multiplier)

Altera Corporation