Resource utilization and performance, Verilog hdl prototype, Resource utilization and performance -2 – Altera Integer Arithmetic IP User Manual

Page 75: Verilog hdl prototype -2

Resource Utilization and Performance

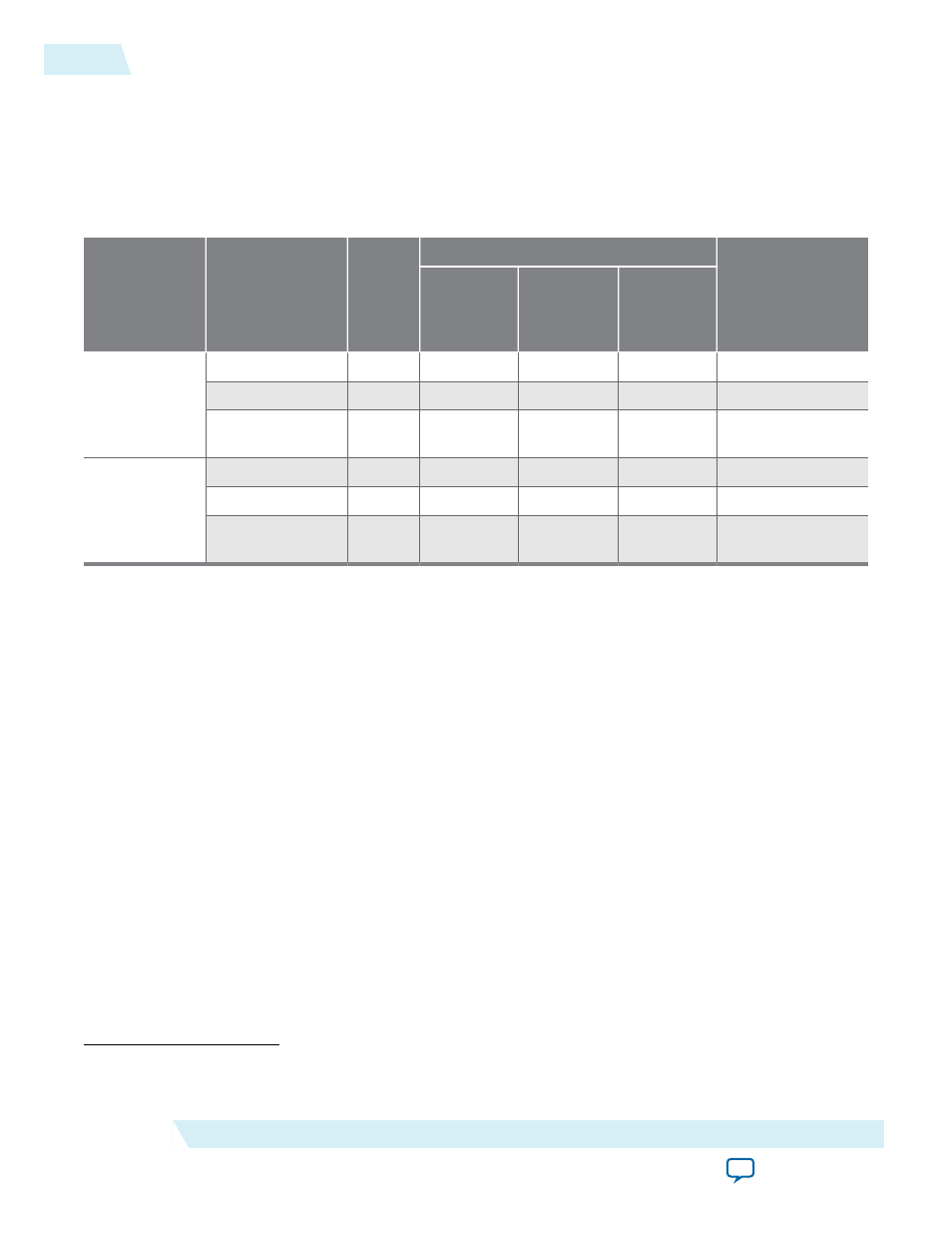

The following table provides resource utilization and performance information for the ALTMEMMULT

megafunction.

Table 7-1: ALTMEMMULT Resource Utilization and Performance

Device family

Input data width

Output

latency

Logic Usage

f

MAX

(MHz)

(4)

Adaptive

Look-Up

Table (ALUT)

Dedicated

Logic

Register

(DLR)

Adaptive

Logic

Module

(ALM)

Stratix III

data(4) × coeff(4) 2

61

62

41

445

data(8) × coeff(8) 7

65

88

55

567

data(16) ×

coeff(16)

7

151

175

107

445

Stratix IV

data(4) × coeff(4) 2

43

55

36

623

data(8) × coeff(8) 7

65

88

56

605

data(16) ×

coeff(16)

7

109

156

96

570

Verilog HDL Prototype

The following Verilog HDL prototype is located in the Verilog Design File (.v) altera_mf.v in the

module altmemmult

#( parameter coeff_representation = "SIGNED",

parameter coefficient0 = "UNUSED",

parameter data_representation = "SIGNED",

parameter intended_device_family = "unused",

parameter max_clock_cycles_per_result = 1,

parameter number_of_coefficients = 1,

parameter ram_block_type = "AUTO",

parameter total_latency = 1,

parameter width_c = 1,

parameter width_d = 1,

parameter width_r = 1,

parameter width_s = 1,

parameter lpm_type = "altmemmult",

parameter lpm_hint = "unused")

( input wire clock,

input wire [width_c-1:0]coeff_in,

input wire [width_d-1:0] data_in,

output wire load_done,

output wire [width_r-1:0] result,

output wire result_valid,

(4)

The performance of the megafunction is dependant on the value of the maximum allowable ceiling f

MAX

that the selected device can achieve. Therefore, results may vary from the numbers stated in this column.

7-2

Resource Utilization and Performance

UG-01063

2014.12.19

Altera Corporation

ALTMEMMULT (Memory-based Constant Coefficient Multiplier)