Design example: 9-bit square root, Understanding the simulation results, Design example: 9-bit square root -4 – Altera Integer Arithmetic IP User Manual

Page 150: Understanding the simulation results -4

Parameter Name

Type

Required

Description

R_PORT_WIDTH

Integer

Yes

Specifies the width of the

remainder[]

output port.

PIPELINE

Integer

No

Specifies the number of clock cycles of latency to add.

LPM_HINT

String

No

When you instantiate a library of parameterized modules

(LPM) function in a VHDL Design File (.vhd), you must

use the

LPM_HINT

parameter to specify an Altera-specific

parameter. For example:

LPM_HINT = "CHAIN_SIZE =

8, ONE_INPUT_IS_CONSTANT = YES"

The default value is

UNUSED

.

LPM_TYPE

String

No

Identifies the library of parameterized modules (LPM)

entity name in VHDL design files.

Design Example: 9-bit Square Root

This design example uses the ALTSQRT megafunction to generate a 9-bit square root. This example uses

the MegaWizard Plug-In Manager in the Quartus II software.

altsqrt.qar (archived Quartus II design files)

altsqrt_ex_msim (ModelSim-Altera files)

Understanding the Simulation Results

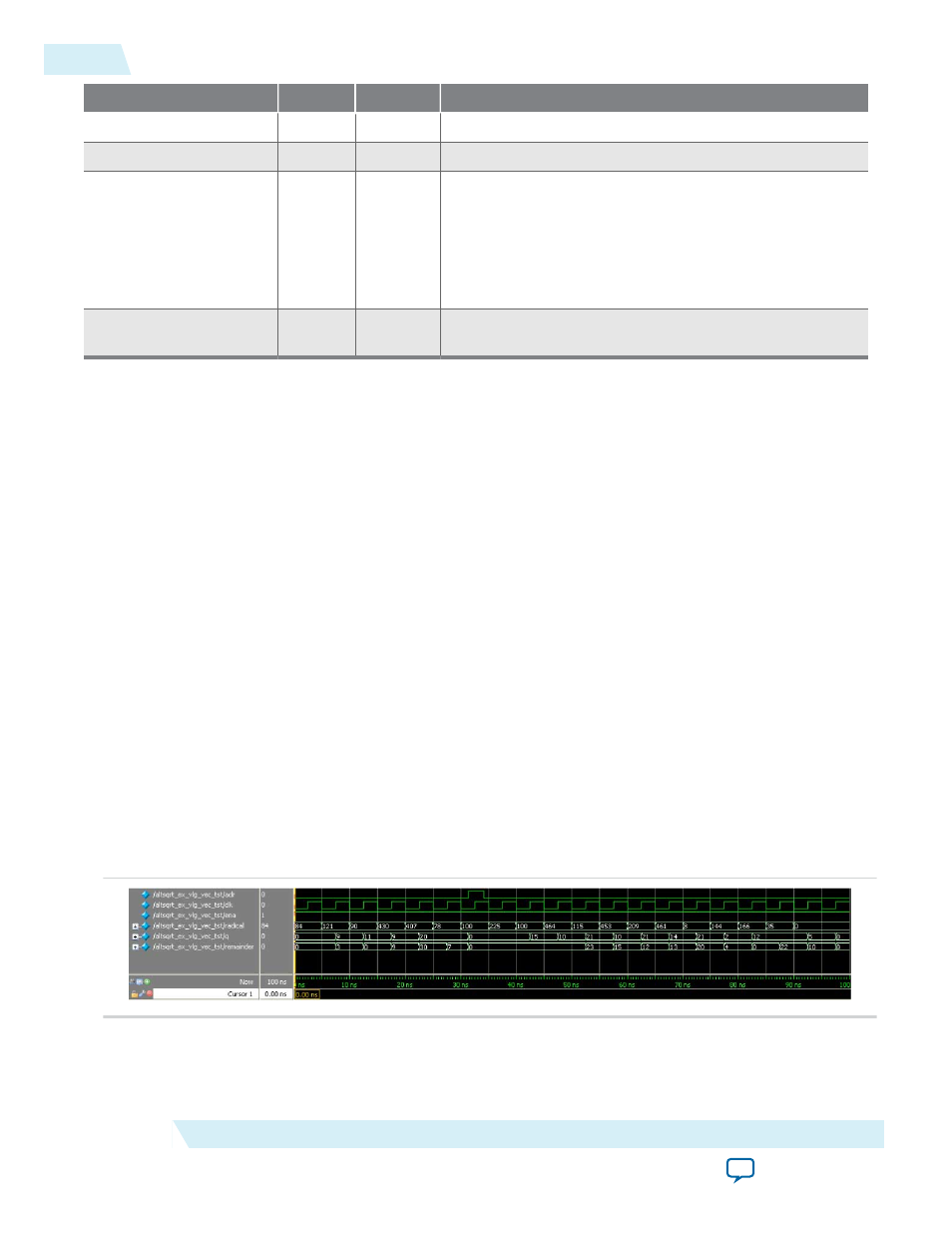

The following settings are observed in this example:

• The width of the input port, radical[], is set to 9 bits.

• The widths of the output ports, q[] and remainder[], are set to 5 bits and 6 bits respectively.

• The asynchronous clear (aclr) and clock enable (ena) input ports are enabled.

• The output latency is set to two clock cycles. Hence, the result is seen on the q[] port two clock cycles

after the input data is available.

The following figure shows the expected simulation results in the ModelSim-Altera software.

Figure 11-2: ALTSQRT Simulation Results

11-4

Design Example: 9-bit Square Root

UG-01063

2014.12.19

Altera Corporation

ALTSQRT (Integer Square Root)