Altecc_encoder features, Altecc_encoder features -2 – Altera Integer Arithmetic IP User Manual

Page 40

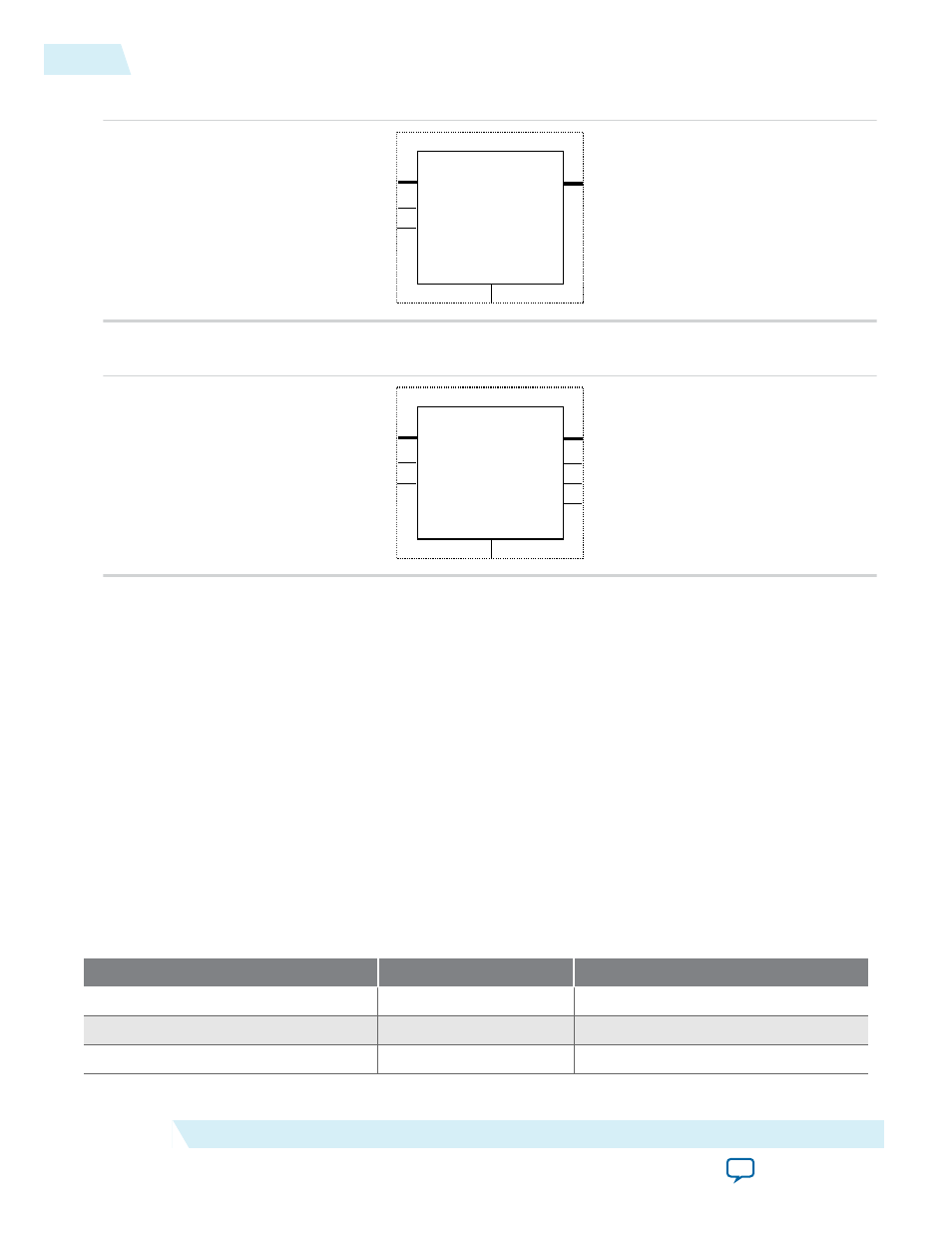

Figure 5-1: ALTECC_ENCODER Ports

data[]

inst

ALTECC_ENCODER

clocken

clock

q[]

aclr

Figure 5-2: ALTECC_DECODER Ports

data[]

inst

ALTECC_DECODER

clocken

clock

q[]

aclr

err_detected

err_corrected

err_fatal

ALTECC_ENCODER Features

The ALTECC_ENCODER megafunction offers the following features:

• Performs data encoding using the Hamming Coding scheme

• Supports data width of 2–64 bits

• Supports signed and unsigned data representation format

• Support pipelining with output latency of either one or two clock cycles

• Supports optional asynchronous clear and clock enable ports

The ALTECC_ENCODER megafunction takes in and encodes the data using the Hamming Coding

scheme. The Hamming Coding scheme derives the parity bits and appends them to the original data to

produce the output code word. The number of parity bits appended depends on the width of the data.

The following table lists the number of parity bits appended for different ranges of data widths. The Total

Bits column represents the total number of input data bits and appended parity bits.

Table 5-1: Number of Parity Bits and Code Word According to Data Width

Data Width

Number of Parity Bits

Total Bits (Code Word)

2-4

3+1

6-8

5-11

4+1

10-16

12-26

5+1

18-32

5-2

ALTECC_ENCODER Features

UG-01063

2014.12.19

Altera Corporation

ALTECC (Error Correction Code: Encoder/Decoder)