Verilog hdl prototype (altecc_encoder), Verilog hdl prototype (altecc_decoder), Verilog hdl prototype (altecc_encoder) -5 – Altera Integer Arithmetic IP User Manual

Page 43: Verilog hdl prototype (altecc_decoder) -5

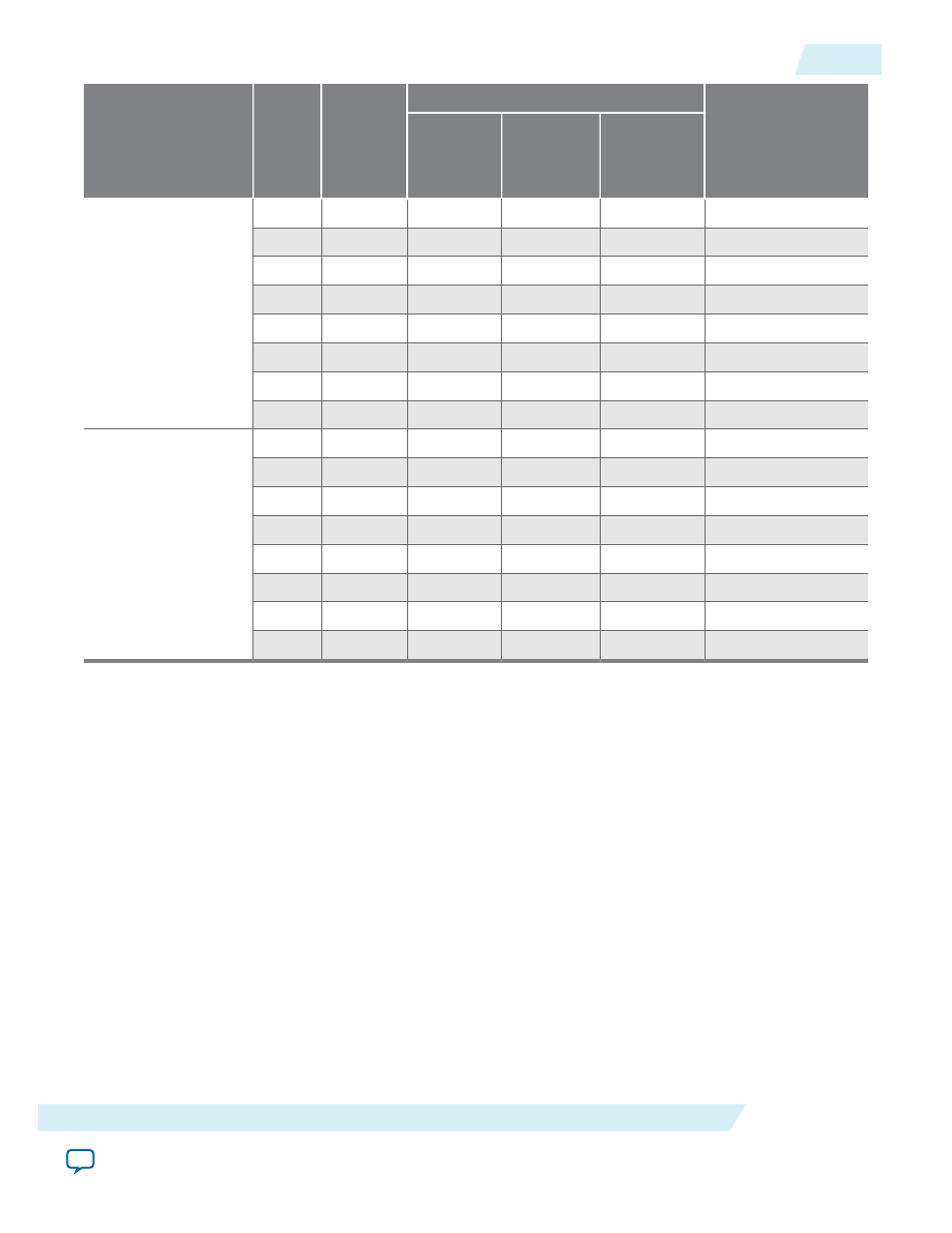

Configuration

Input

data

width

Output

latency

Logic Usage

f

MAX

(MHz)

Adaptive

Look-Up

Table

(ALUT)

Dedicated

Logic

Register

(DLR)

Adaptive

Logic Module

(ALM)

ALTECC_

ENCODER

12

0

8

0

4

1128

29

0

21

0

13

1072

32

0

19

0

12

1054

64

0

40

0

27

901

12

2

8

30

19

1104

29

2

20

65

38

1082

32

2

19

71

42

1061

64

2

39

136

78

905

ALTECC_

DECODER

12

0

8

0

4

1128

29

0

21

0

13

1072

32

0

19

0

12

1054

64

0

40

0

27

901

12

2

8

30

19

1104

29

2

20

65

38

1082

32

2

19

71

42

1061

64

2

39

136

78

905

Verilog HDL Prototype (ALTECC_ENCODER)

The following Verilog HDL prototype is located in the Verilog Design File (.v) lpm.v in the

installation directory>\eda\synthesis directory.

module altecc_encoder

#( parameter intended_device_family = "unused",

parameter lpm_pipeline = 0,

parameter width_codeword = 8,

parameter width_dataword = 8,

parameter lpm_type = "altecc_encoder",

parameter lpm_hint = "unused")

( input wire aclr,

input wire clock,

input wire clocken,

input wire [width_dataword-1:0] data,

output wire [width_codeword-1:0] q);

endmodule

Verilog HDL Prototype (ALTECC_DECODER)

UG-01063

2014.12.19

Verilog HDL Prototype (ALTECC_ENCODER)

5-5

ALTECC (Error Correction Code: Encoder/Decoder)

Altera Corporation