Vhdl library_use declaration, Ports, Vhdl library_use declaration -3 – Altera Integer Arithmetic IP User Manual

Page 153: Ports -3

The VHDL component declaration is located in the VHDL Design File (.vhd)

altera_mf_components.vhd in the

\libraries\vhdl\altera_mf

directory.

component parallel_add

generic (

width : natural := 4;

size : natural := 2;

widthr : natural := 4;

shift : natural := 0;

msw_subtract : string := "NO";

representation : string := "UNSIGNED";

pipeline : natural := 0;

result_alignment : string := "LSB";

lpm_hint: string := "UNUSED";

lpm_type : string := "parallel_add");

port (

data:in altera_mf_logic_2D(size - 1 downto 0,width- 1 downto 0);

clock : in std_logic := '1';

aclr : in std_logic := '0';

clken : in std_logic := '1';

result : out std_logic_vector(widthr - 1 downto 0));

end component;

VHDL LIBRARY_USE Declaration

The VHDL LIBRARY-USE declaration is not required if you use the VHDL Component Declaration.

LIBRARY altera_mf;

USE altera_mf.altera_mf_components.all;

Ports

The following tables list the input and output ports of the PARALLEL_ADD megafunction.

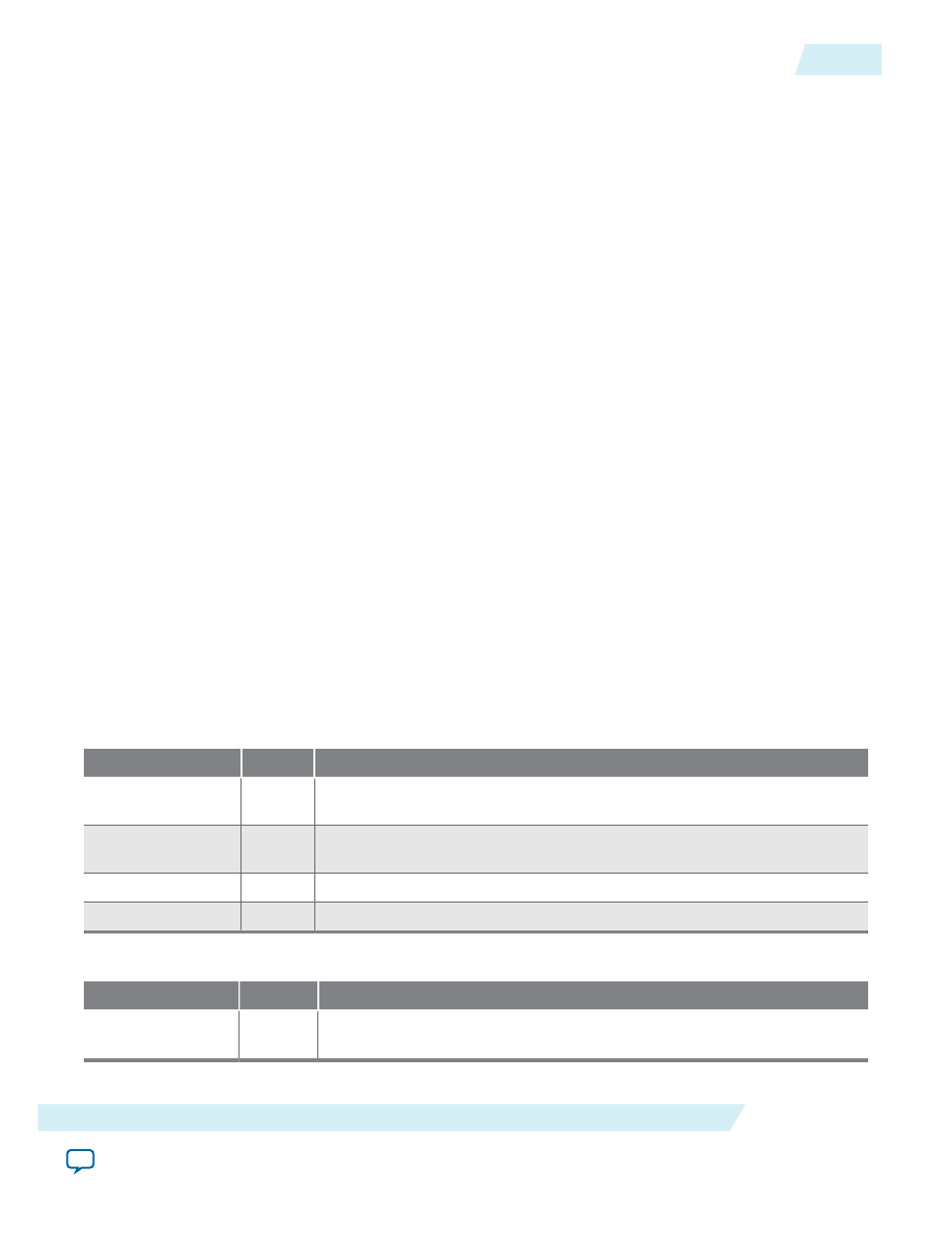

Table 12-2: PARALLEL_ADD Megafunction Input Ports

Port Name

Required

Description

data[]

Yes

Data input to the parallel adder. Input port

[SIZE - 1 DOWNTO 0, WIDTH-

1 DOWNTO 0]

wide.

clock

No

Clock input to the parallel adder. This port is required if the

PIPELINE

parameter has a value of greater than

0

.

clken

No

Clock enable to the parallel adder. If omitted, the default value is

1

.

aclr

No

Active high asynchronous clear input to the parallel adder.

Table 12-3: PARALLEL_ADD Megafunction Output Ports

Port Name

Required

Description

result[]

Yes

Adder output port. The size of the output port depends on the

WIDTHR

parameter value.

UG-01063

2014.12.19

VHDL LIBRARY_USE Declaration

12-3

PARALLEL_ADD (Parallel Adder)

Altera Corporation