Verilog hdl prototype, Verilog hdl prototype -2 – Altera Integer Arithmetic IP User Manual

Page 33

The LPM_MULT megafunction can be implemented using either logic resources or dedicated multiplier

circuitry in Altera devices. Typically, the LPM_MULT megafunction is translated to the dedicated

multiplier circuitry when it is available because it provides better performance and resource utilization. If

all of the input data widths are smaller than or equal to nine bits, the function uses the 9 × 9 multiplier

configuration in the dedicated multiplier. Otherwise, 18 × 18 multipliers are used to process data with

widths between 10 bits and 18 bits.

For information about the architecture of the DSP blocks and embedded multipliers, and for detailed

information about the hardware conversion process, refer to the DSP block and embedded multiplier

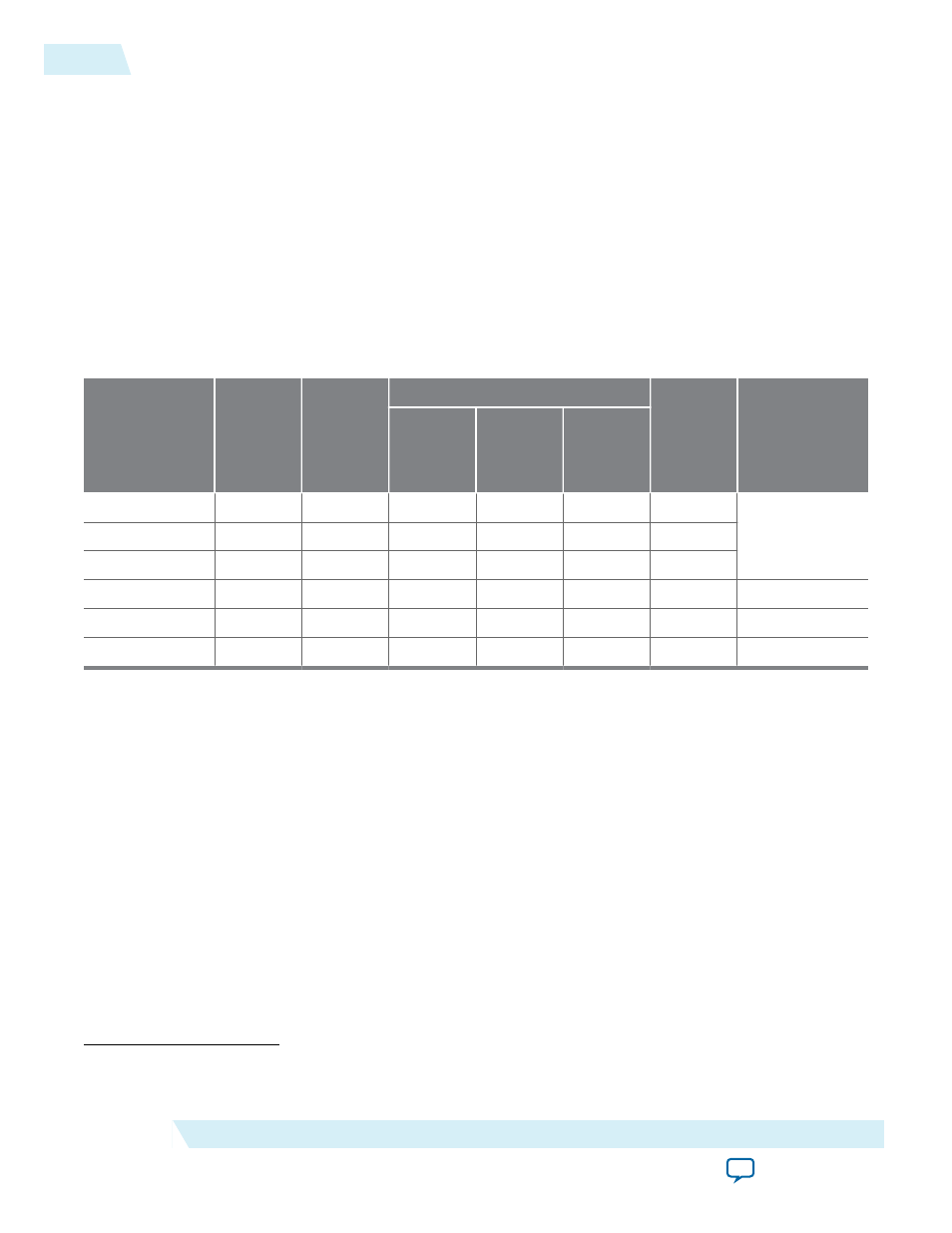

The following table provides resource utilization and performance information for the LPM_MULT

megafunction.

Table 4-1: LPM_MULT Resource Utilization and Performance

Device family

Input data

width

Output

latency

Logic Usage

18-bit DSP

f

MAX

(MHz)

(2)

Adaptive

Look-Up

Table

(ALUT)

Dedicated

Logic

Register

(DLR)

Adaptive

Logic

Module

(ALM)

Stratix III

8 × 8

0

0

0

0

1

N/A

16 × 16

0

0

0

0

2

32 × 32

0

0

0

0

4

16 × 16

3

0

0

0

2

645

32 × 32

3

0

0

0

4

454

64 × 64

3

92

128

82

16

191

Verilog HDL Prototype

The following Verilog HDL prototype is located in the Verilog Design File (.v) lpm.v in the

installation directory>\eda\synthesis directory.

module lpm_mult ( result, dataa, datab, sum, clock, clken, aclr )

parameter lpm_type = "lpm_mult";

parameter lpm_widtha = 1;

parameter lpm_widthb = 1;

parameter lpm_widths = 1;

parameter lpm_widthp = 1;

parameter lpm_representation = "UNSIGNED";

parameter lpm_pipeline = 0;

parameter lpm_hint = "UNUSED";

input clock;

input clken;

input aclr;

input [lpm_widtha-1:0] dataa;

input [lpm_widthb-1:0] datab;

(2)

The performance of the megafunction is dependant on the value of the maximum allowable ceiling f

MAX

that the selected device can achieve. Therefore, results may vary from the numbers stated in this column.

4-2

Verilog HDL Prototype

UG-01063

2014.12.19

Altera Corporation

LPM_MULT (Multiplier)