Verilog hdl prototype, Vhdl component declaration, Vhdl library_use declaration – Altera Integer Arithmetic IP User Manual

Page 63: Ports, Verilog hdl prototype -10, Vhdl component declaration -10, Vhdl library_use declaration -10, Ports -10

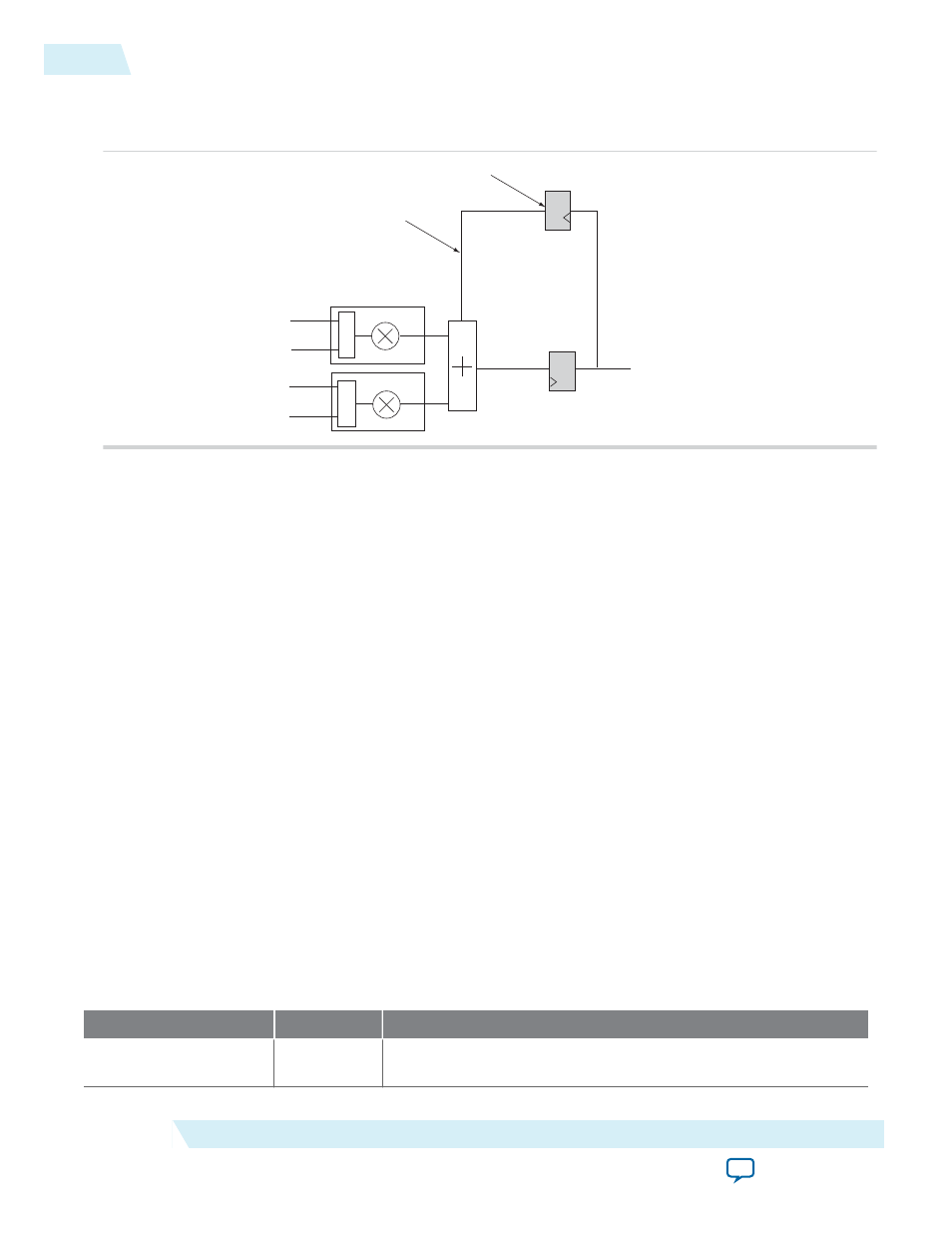

The following figure shows the double accumulator implementation.

Figure 6-12: Double Accumulator

a0

b0

a1

b1

Mult0

Mult1

Accu mulator feedba ck

Output result

+/-

+/-

Dou ble Accu mulator Register

Output Register

Verilog HDL Prototype

The following Verilog HDL prototype is located in the Verilog Design File (.v) in the

tion directory>\eda\synthesis directory.

VHDL Component Declaration

The VHDL component declaration is located in the VHDL Design File (.vhd) in the

tion directory> directory.

VHDL LIBRARY_USE Declaration

The VHDL LIBRARY-USE declaration is not required if you use the VHDL Component Declaration.

LIBRARY altera_mf;

USE altera_mf.altera_mf_components.all;

Ports

The following tables list the input and output ports of the ALTERA_MULT_ADD megafunction.

Table 6-1: ALTERA_MULT_ADD MegaFunction Input Ports

Port name

Required

Description

dataa []

Yes

Data input to the multiplier. Input port

[NUMBER_OF_

MULTIPLIERS * WIDTH_A - 1 … 0]

wide

6-10

Verilog HDL Prototype

UG-01063

2014.12.19

Altera Corporation

ALTERA_MULT_ADD (Multiply-Adder)