Vhdl component declaration, Vhdl library_use declaration, Lpm_mult ports – Altera Integer Arithmetic IP User Manual

Page 34: Vhdl component declaration -3, Vhdl library_use declaration -3, Lpm_mult ports -3

input [lpm_widths-1:0] sum;

output [lpm_widthp-1:0] result;

endmodule

VHDL Component Declaration

The VHDL component declaration is located in the VHDL Design File (.vhd) LPM_PACK.vhd in the

\libraries\vhdl\lpm

directory.

component LPM_MULT

generic ( LPM_WIDTHA : natural;

LPM_WIDTHB : natural;

LPM_WIDTHS : natural := 1;

LPM_WIDTHP : natural;

LPM_REPRESENTATION : string := "UNSIGNED";

LPM_PIPELINE : natural := 0;

LPM_TYPE: string := L_MULT;

LPM_HINT : string := "UNUSED");

port ( DATAA : in std_logic_vector(LPM_WIDTHA-1 downto 0);

DATAB : in std_logic_vector(LPM_WIDTHB-1 downto 0);

ACLR : in std_logic := '0';

CLOCK : in std_logic := '0';

CLKEN : in std_logic := '1';

SUM : in std_logic_vector(LPM_WIDTHS-1 downto 0) := (OTHERS => '0');

RESULT : out std_logic_vector(LPM_WIDTHP-1 downto 0));

end component;

VHDL LIBRARY_USE Declaration

The VHDL LIBRARY-USE declaration is not required if you use the VHDL Component Declaration.

LIBRARY lpm;

USE lpm.lpm_components.all;

LPM_MULT Ports

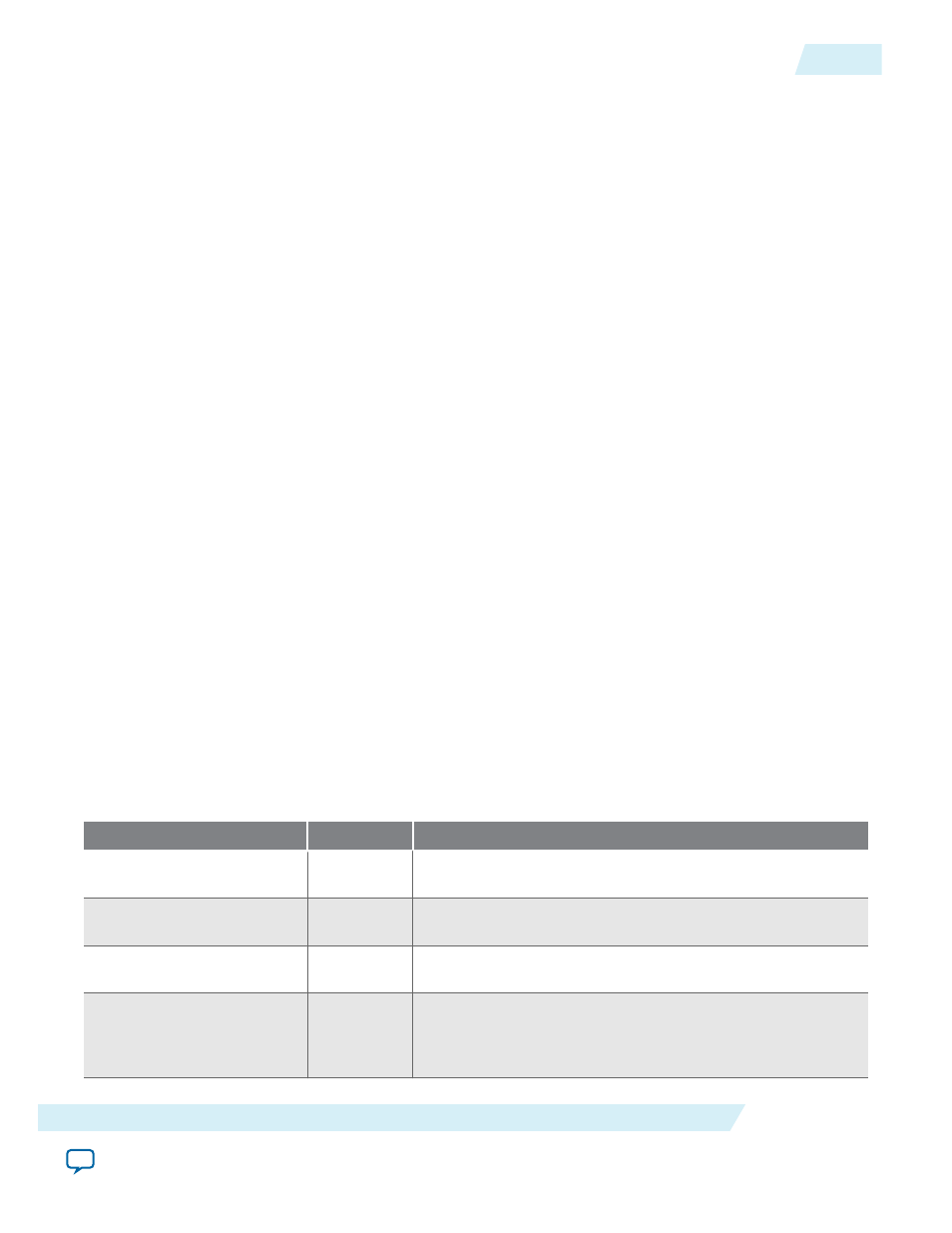

Table 4-2: LPM_MULT IP Core Input Ports

Port Name

Required

Description

dataa[]

Yes

Data input. The size of the input port depends on the

LPM_

WIDTHA

parameter value.

datab[]

Yes

Data input. The size of the input port depends on the

LPM_

WIDTHB

parameter value.

clock

No

Clock input for pipelined usage. For

LPM_PIPELINE

values

other than

0

(default), the clock port must be enabled.

clken

No

Clock enable for pipelined usage. When the

clken

port is

asserted high, the adder/subtractor operation takes place.

When the signal is low, no operation occurs. If omitted, the

default value is

1

.

UG-01063

2014.12.19

VHDL Component Declaration

4-3

LPM_MULT (Multiplier)

Altera Corporation