Altera Integer Arithmetic IP User Manual

Page 72

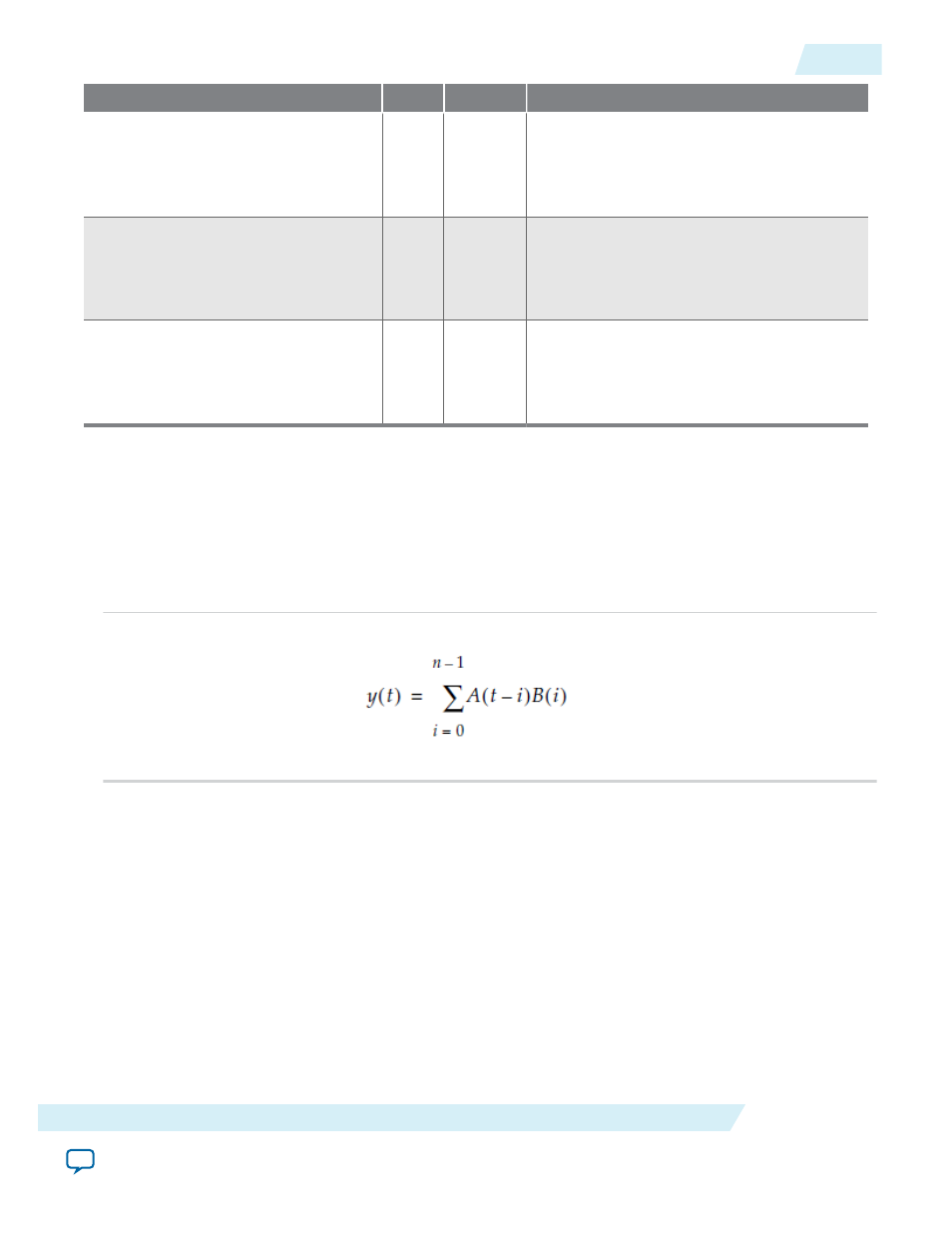

Parameter Name

Type

Required

Description

ADDNSUB_MULTIPLIER_LATENCY_

ACLR[]

String No

Parameter

[1, 3]

. Specifies the asynchro‐

nous clear signal for the pipeline register on

the corresponding

addnsub[]

input. Values

are

NONE

,

ACLR0

and

ACLR1

. If omitted, the

default value is

NONE.

ACCUM_SLOAD_LATENCY_CLOCK

String No

Specifies the clock signal for the pipeline

register on the corresponding

accum_sload

or

sload_accum

input. Values are

UNREGIS-

TERED

,

CLOCK0

,

CLOCK1

and

CLOCK2

. If

omitted, the default value is

UNREGISTERED.

ACCUM_SLOAD_LATENCY_ACLR

String No

Specifies the asynchronous clear signal for

the pipeline register on the corresponding

accum_sload

or

sload_accum

input. Values

are

NONE

,

ACLR0

and

ACLR1

. If omitted, the

default value is

NONE.

Design Example: Implementing a Simple Finite Impulse Response (FIR)

Filter

This design example uses the ALTMULT_ADD megafunction to implement a simple FIR filter as shown

in the following equation. This example uses the MegaWizard Plug-In Manager in the Quartus II

software.

n represents the number of taps, A(t) represents the sequence of input samples, and B(i) represents the

filter coefficients.

The number of taps (n) can be any value, but this example is of a simple FIR filter with n = 4, which is

called a 4-tap filter. To implement this filter, the coefficients of data B is loaded into the B registers in

parallel and a

shiftin

register moves data A(0) to A(1) to A(2), and so on. With a 4-tap filter, at a given

time (t), the sum of four products is computed. This function is implemented using the shift register chain

option in the ALTMULT_ADD megafunction.

With reference to the equation, input B represents the coefficients and data A represents the data that is

shifted into. The A input (data) is shifted in with the main clock, named

clock0

. The B input

(coefficients) is loaded at the rising edge of

clock1

with the enable signal held high.

:

fir_fourtap.qar (archived Quartus II design files)

UG-01063

2014.12.19

Design Example: Implementing a Simple Finite Impulse Response (FIR) Filter

6-19

ALTERA_MULT_ADD (Multiply-Adder)

Altera Corporation