Resource utilization and performance, Verilog hdl prototype, Resource utilization and performance -2 – Altera Integer Arithmetic IP User Manual

Page 20: Verilog hdl prototype -2

Resource Utilization and Performance

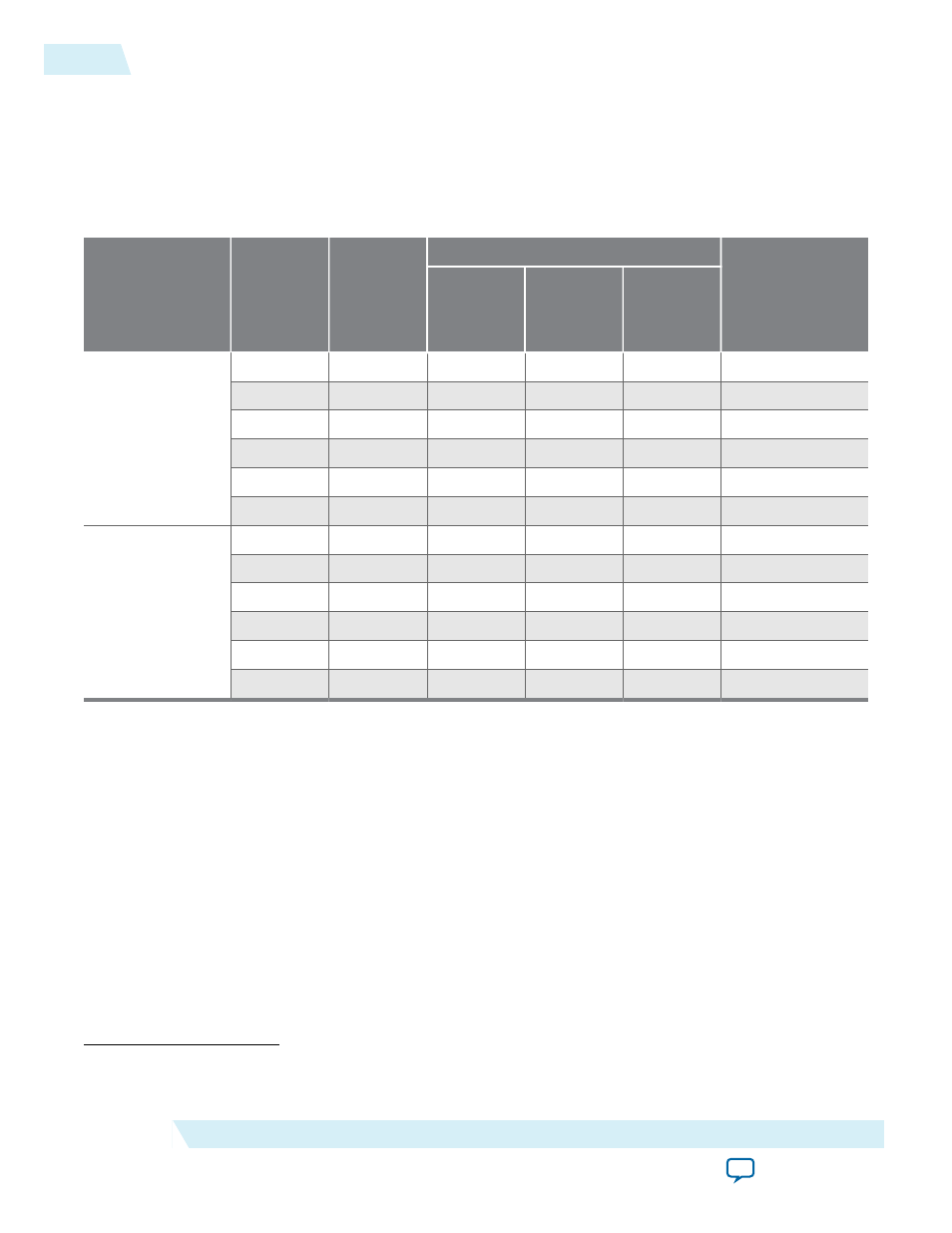

The following table provides resource utilization and performance information for the LPM_COUNTER

megafunction.

Table 2-1: LPM_COUNTER Resource Utilization and Performance

Device family

Input data

width

Output

latency

Logic Usage

f

MAX

(MHz)

(1)

Adaptive

Look-Up

Table (ALUT)

Dedicated

Logic

Register

(DLR)

Adaptive

Logic

Module

(ALM)

Stratix III

4

-

9

4

6

723

8

-

9

8

5

808

16

-

17

16

9

705

24

-

25

24

13

583

32

-

33

32

17

489

64

-

65

64

33

329

Stratix IV

4

-

9

4

6

768

8

-

9

8

5

896

16

-

17

16

9

825

24

-

25

24

13

716

32

-

33

32

17

639

64

-

65

64

33

470

Verilog HDL Prototype

The following Verilog HDL prototype is located in the Verilog Design File (.v) lpm.v in the

installation directory>\eda\synthesis directory.

module lpm_counter ( q, data, clock, cin, cout, clk_en, cnt_en, updown,

aset, aclr, aload, sset, sclr, sload, eq );

parameter lpm_type = "lpm_counter";

parameter lpm_width = 1;

parameter lpm_modulus = 0;

parameter lpm_direction = "UNUSED";

parameter lpm_avalue = "UNUSED";

parameter lpm_svalue = "UNUSED";

parameter lpm_pvalue = "UNUSED";

parameter lpm_port_updown = "PORT_CONNECTIVITY";

parameter lpm_hint = "UNUSED";

output [lpm_width-1:0] q;

(1)

The performance of the megafunction is dependant on the value of the maximum allowable ceiling f

MAX

that the selected device can achieve. Therefore, results may vary from the numbers stated in this column.

2-2

Resource Utilization and Performance

UG-01063

2014.12.19

Altera Corporation

LPM_COUNTER (Counter)