Lpm_mult parameters, Lpm_mult parameters -4 – Altera Integer Arithmetic IP User Manual

Page 35

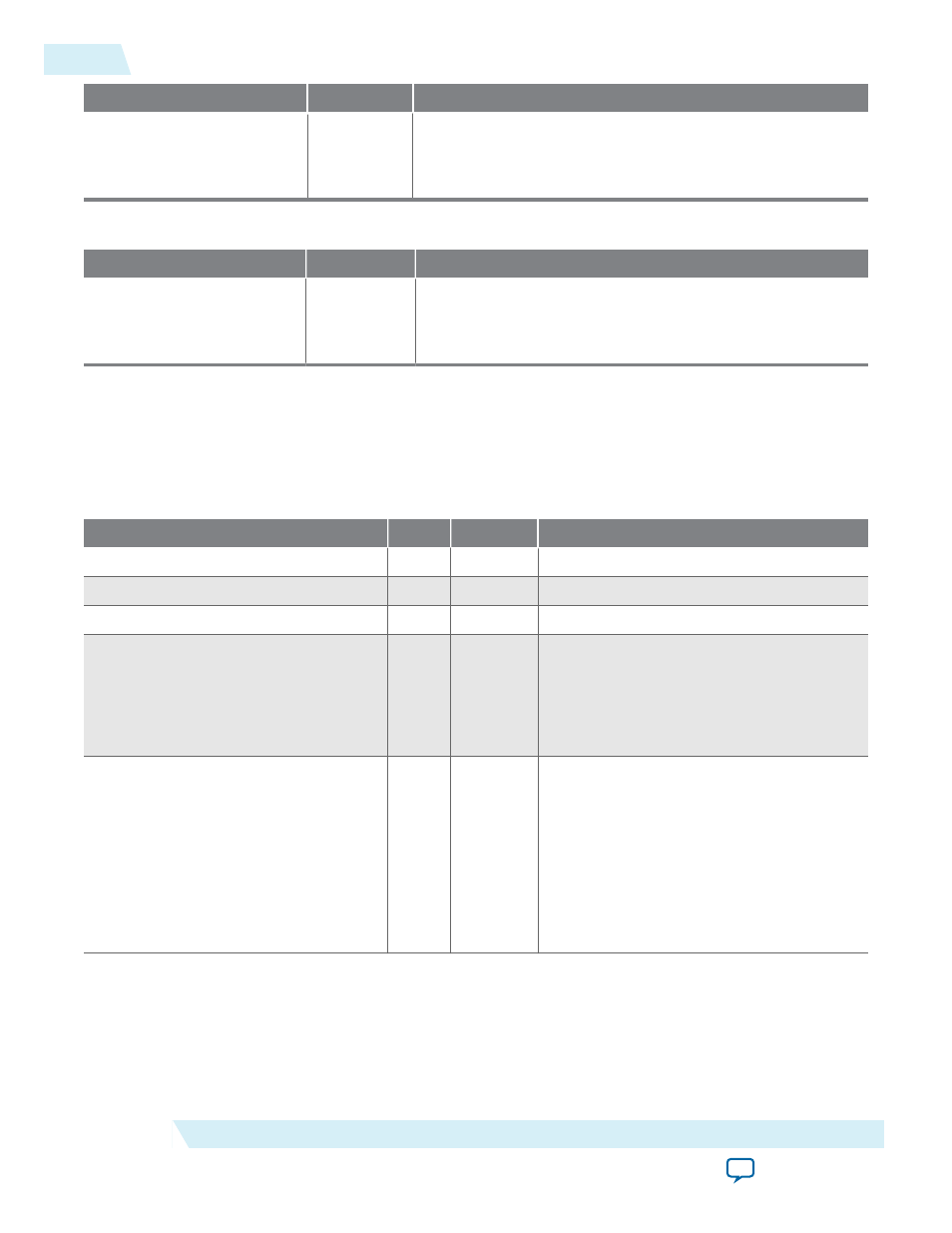

Port Name

Required

Description

aclr

No

Asynchronous clear port used at any time to reset the

pipeline to all

0

s, asynchronously to the clock signal. The

pipeline initializes to an undefined (X) logic level. The

outputs are a consistent, but non-zero value.

Table 4-3: LPM_MULT IP Core Output Ports

Port Name

Required

Description

result[]

Yes

Data output. The size of the output port depends on the

LPM_WIDTHP

parameter value. If

LPM_WIDTHP

< max (

LPM_

WIDTHA

+

LPM_WIDTHB

,

LPM_WIDTHS

) or (

LPM_WIDTHA

+

LPM_

WIDTHS

), only the

LPM_WIDTHP

MSBs are present.

LPM_MULT Parameters

The following table lists the parameters for the LPM_MULT megafunction.

Table 4-4: LPM_MULT Megafunction Parameters

Parameter Name

Type

Required

Description

LPM_WIDTHA

Integer Yes

Specifies the width of the

dataa[]

port.

LPM_WIDTHB

Integer Yes

Specifies the width of the

datab[]

port.

LPM_WIDTHP

Integer Yes

Specifies the width of the

result[]

port.

LPM_REPRESENTATION

String No

Specifies the type of multiplication

performed. Values are

SIGNED

and

UNSIGNED

. If omitted, the default value is

UNSIGNED

. When this parameter value is

set to

SIGNED

, the multiplier interprets the

data input as signed two's complement.

LPM_PIPELINE

String No

Specifies the number of latency clock

cycles associated with the

result[]

output. A value of zero (

0

) indicates that

no latency exists, and that a purely

combinational function will be instanti‐

ated. For Stratix and Stratix GX devices, if

the design uses DSP blocks, you can

increase the performance of the design

when the value of the

LPM_PIPELINE

parameter is 3 or less.

4-4

LPM_MULT Parameters

UG-01063

2014.12.19

Altera Corporation

LPM_MULT (Multiplier)