Jtag pins, Internal configuration, Internal configuration modes – Altera MAX 10 FPGA User Manual

Page 6: Internal configuration -2

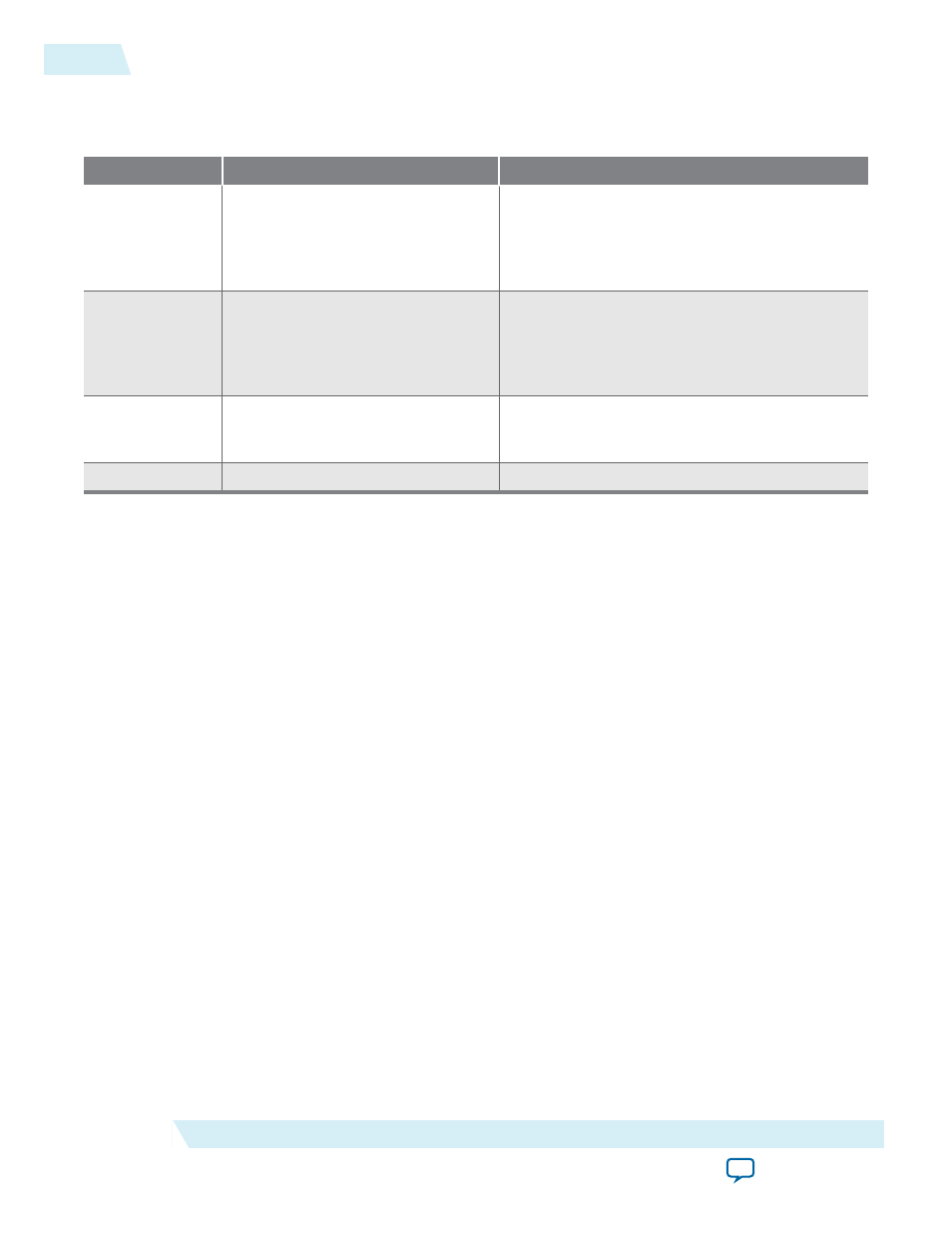

JTAG Pins

Table 2-1: JTAG Pin

Pin

Function

Description

TDI

Serial input pin for:

• instructions

• test data

• programming data

•

TDI

is sampled on the rising edge of

TCK

•

TDI

pins have internal weak pull-up resistors.

TDO

Serial output pin for:

• instructions

• test data

• programming data

•

TDO

is sampled on the falling edge of

TCK

• The pin is tri-stated if data is not shifted out

of the device.

TMS

Input pin that provides the control

signal to determine the transitions of

the TAP controller state machine.

•

TMS

is sampled on the rising edge of

TCK

•

TMS

pins have internal weak pull-up resistors.

TCK

Clock input to the BST circuitry.

—

All the JTAG pins are powered by the V

CCIO

1B. In JTAG mode, the I/O pins support the LVTTL/

LVCMOS 3.3-1.5V standards.

Related Information

•

Provides more information about supported I/O standard in MAX 10 devices.

•

Guidelines: Dual-Purpose Configuration Pin

on page 3-1

•

on page 3-2

Internal Configuration

You need to program the configuration data into the configuration flash memory (CFM) before internal

configuration can take place. The configuration data to be written to CFM will be part of the programmer

object file (

.pof

). Using JTAG In-System Programming (ISP), you can program the

.pof

into the internal

flash.

During internal configuration, MAX 10 devices load the CRAM with configuration data from the CFM.

Internal Configuration Modes

The internal configuration scheme for all MAX 10 devices except for 10M02 device consists of the

following modes:

• Dual Compressed Images—configuration image is stored as image 0 and image 1 in the CFM

• Single Compressed Image

• Single Compressed Image with Memory Initialization

• Single Uncompressed Image

• Single Uncompressed Image with Memory Initialization

In dual compressed images mode, you can use the

CONFIG_SEL

pin to select the configuration image.

2-2

JTAG Pins

UG-M10CONFIG

2015.05.04

Altera Corporation

MAX 10 FPGA Configuration Schemes and Features