Jtag secure mode instructions, Verify protect, Jtag instruction availability – Altera MAX 10 FPGA User Manual

Page 21

Related Information

•

on page 2-17

•

Configuration Flash Memory Permissions

on page 2-18

•

.pof Generation through Convert Programming Files

on page 3-6

JTAG Secure Mode Instructions

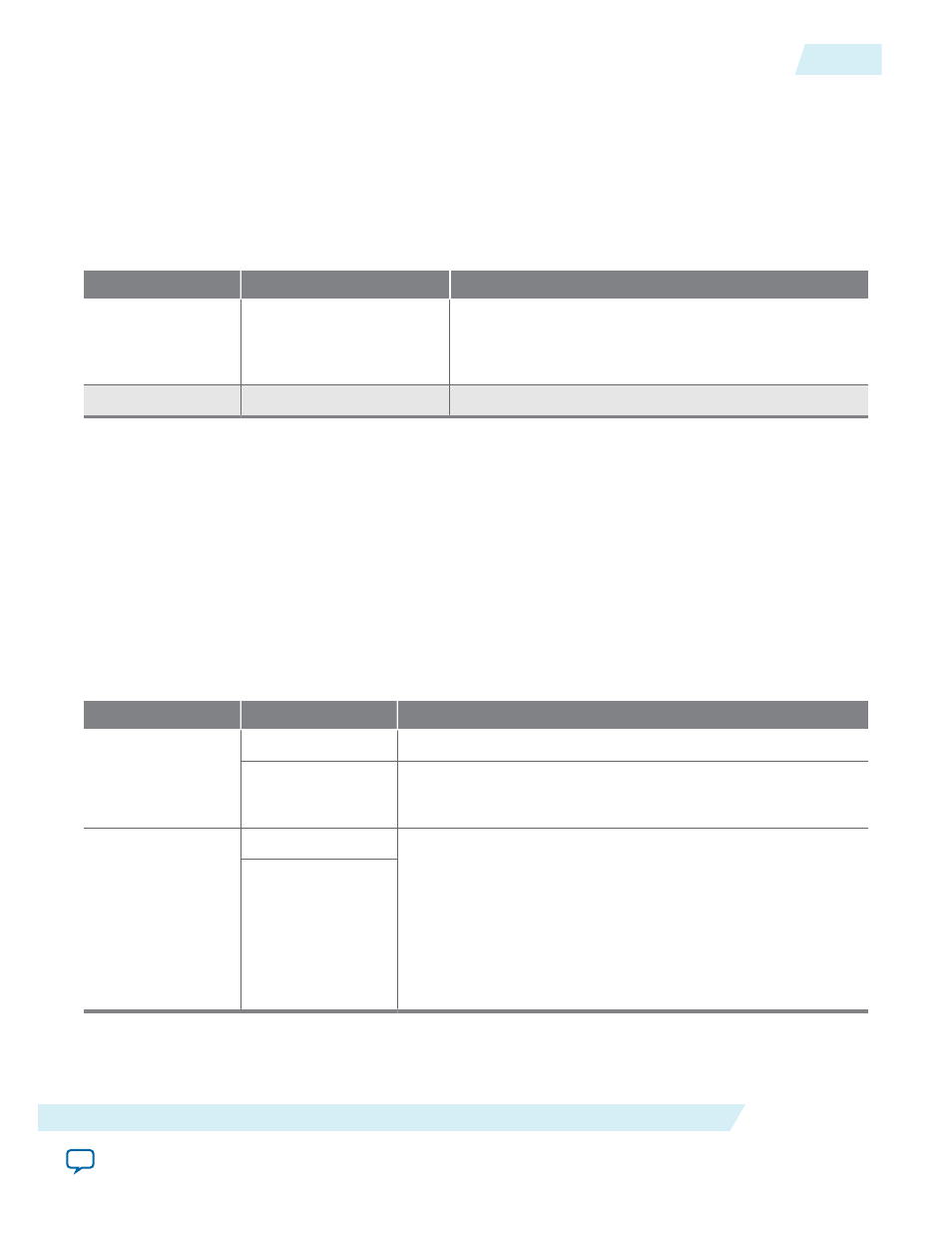

Table 2-12: JTAG Secure Mode Instructions for MAX 10 Devices

JTAG Instruction

Instruction Code

Description

LOCK

10 0000 0010

• Activates the JTAG secure mode.

• Blocks access from both external pins and core to

JTAG.

UNLOCK

10 0000 1000

Deactivates the JTAG secure mode.

Verify Protect

Verify Protect is a security feature to enhance CFM security. When you enable the Verify Protect, only

program and erase operation are allowed on the CFM. This capability protects the CFM contents from

being copied.

You can turn on the Verify Protect feature by enabling the Verify Protect in the Quartus II programmer.

Related Information

Configuration Flash Memory Permissions

JTAG Instruction Availability

Table 2-13: JTAG Instruction Availability Based on JTAG Secure Mode and Encryption Settings

JTAG Secure Mode

Encryption

Description

Disabled

Disabled

All JTAG Instructions enabled

Enabled

All JTAG Instructions are enabled except:

•

CONFIGURE

Enabled

Disabled

All JTAG Instructions are disabled except:

•

SAMPLE/PRELOAD

•

BYPASS

•

EXTEST

•

IDCODE

•

UNLOCK

•

LOCK

Enabled

Related Information

•

on page 2-16

UG-M10CONFIG

2015.05.04

JTAG Secure Mode Instructions

2-17

MAX 10 FPGA Configuration Schemes and Features

Altera Corporation