Configuration flash memory permissions, Seu mitigation and configuration error detection – Altera MAX 10 FPGA User Manual

Page 22

•

on page 2-15

Configuration Flash Memory Permissions

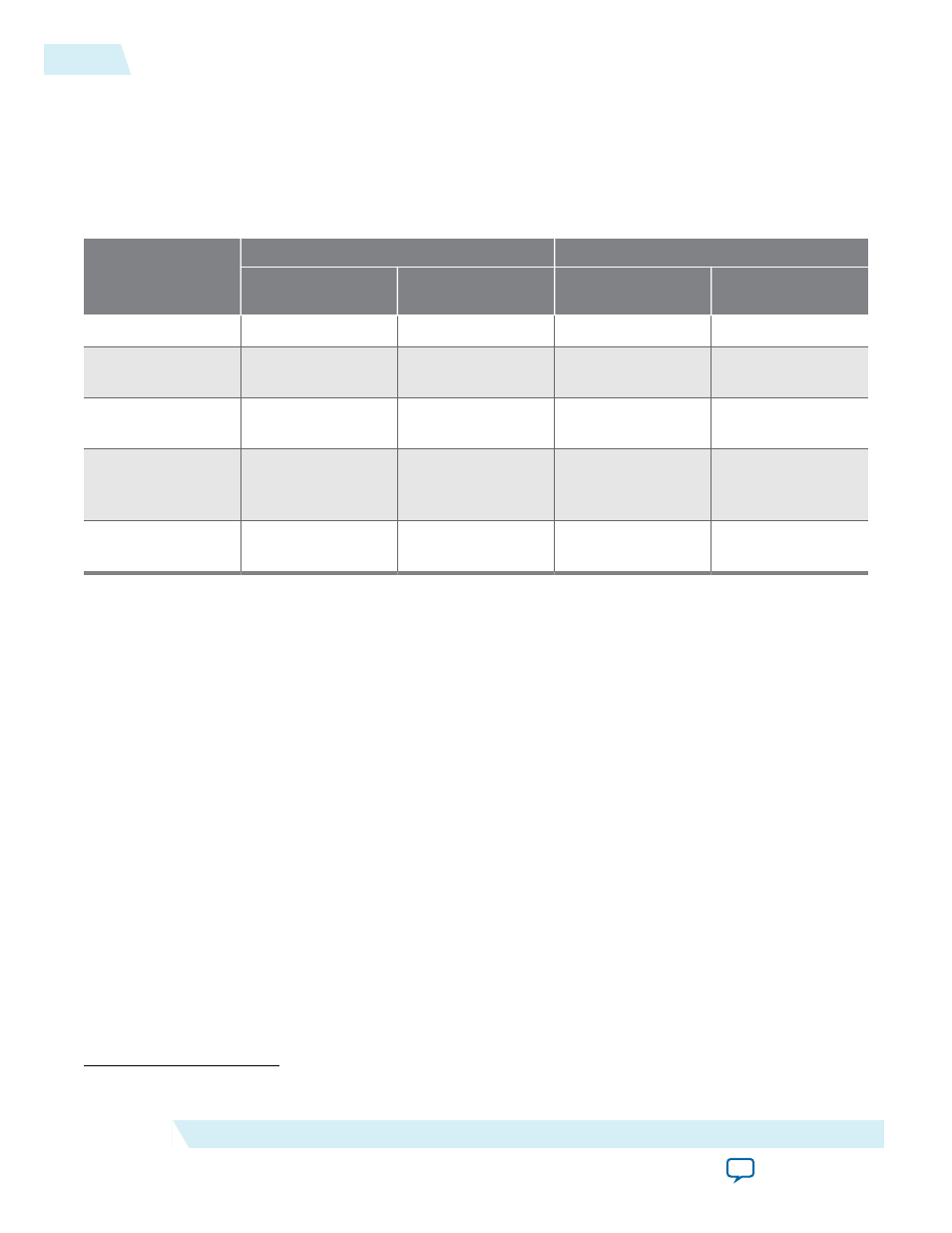

The JTAG secure mode and verify protect features determines the CFM operation permission.. The table

list the operations permitted based on the security settings.

Table 2-14: CFM Permissions for MAX 10 Devices

Operation

JTAG Secure Mode Disabled

JTAG Secure Mode Enabled

Verify Protect

Disabled

Verify Protect

Enabled

Verify Protect

Disabled

Verify Protect

Enabled

ISP through core Illegal operation

Illegal operation

Illegal operation

Illegal operation

ISP through

JTAG pins

Full access

Program and erase

only

No access

No access

Real-time ISP

through core

Full access

Program and erase

only

No access

No access

Real-time ISP

through JTAG

pins

Full access

Program and erase

only

No access

No access

UFM interface

through core

(5)

Full access

Full access

Full access

Full access

Related Information

•

on page 2-16

•

SEU Mitigation and Configuration Error Detection

The dedicated circuitry built in MAX 10 devices consists of an error detection cyclic redundancy check

(EDCRC) feature. You can use this feature to mitigate single-event upset (SEU) or soft errors.

The hardened on-chip EDCRC circuitry allows you to perform the following operations without any

impact on the fitting of the device:

• Auto-detection of cyclic redundancy check (CRC) errors during configuration.

• Identification of SEU in user mode with the optional CRC error detection.

• Testing of error detection by error detection verification through the JTAG interface.

Related Information

•

Verifying Error Detection Functionality

•

on page 3-9

•

Accessing Error Detection Block Through User Interface

on page 3-9

(5)

The UFM interface through core is available if you select the dual compressed image mode.

2-18

Configuration Flash Memory Permissions

UG-M10CONFIG

2015.05.04

Altera Corporation

MAX 10 FPGA Configuration Schemes and Features