Altera MAX 10 FPGA User Manual

Page 51

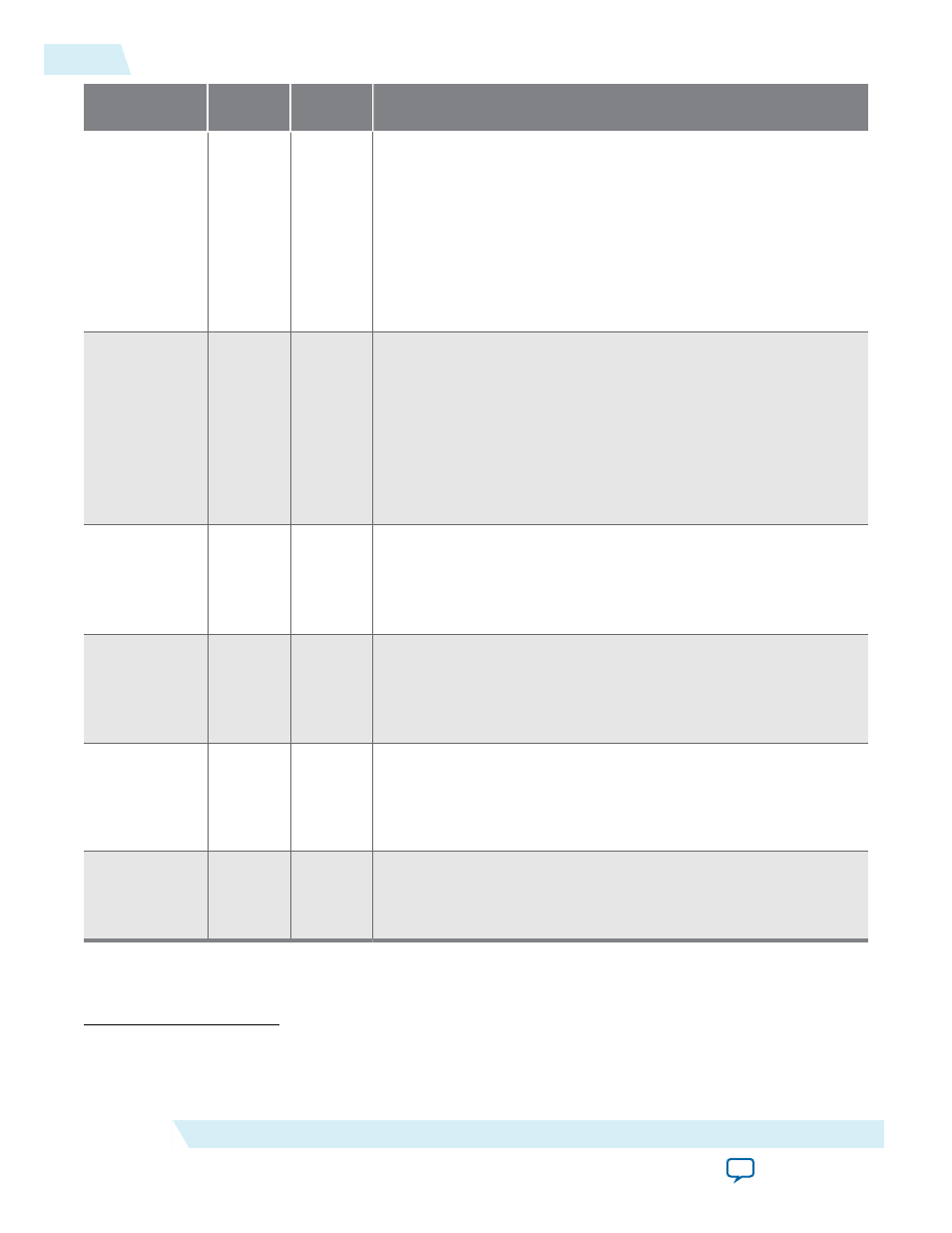

Offset

R/W

Width

(Bits)

Description

2

W

32

• Bit 0—trigger read operation from the user watchdog.

• Bit 1—trigger read operation from the previous state applica‐

tion 2 register.

• Bit 2—trigger read operation from the previous state applica‐

tion 1 register.

• Bit 3—trigger read operation from the input register.

• Bit 31:4—reserved.

The

busy

signal is generated right after the write cycle.

3

R

32

• Bit 0—IP

busy

signal.

• Bit 31:1—reserved.

The

busy

signal indicates the Dual Configuration IP core is in the

writing or reading process. In this state, all write operation to the

remote system upgrade block registers operation request are

ignored except for triggering the reset timer. Altera recommends

you to pull this

busy

signal once you triggered any read or write

process.

4

R

32

• Bit 11:0—user watchdog value.

(10)

• Bit 12—current state of the user watchdog.

• Bit 16:13—

msm_cs

value of the current state.

• Bit 31:17—reserved.

5

R

32

• Bit 3:0—previous state application 1 reconfiguration source

value.

• Bit 7:4—

msm_cs

value of the previous state application 1.

• Bit 31:8—reserved.

6

R

32

• Bit 3:0—previous state application 2 reconfiguration source

value.

• Bit 7:4—

msm_cs

value of the previous state application 2.

• Bit 31:8—reserved.

7

R

32

• Bit 0—

config_sel_overwrite

value from the input register.

• Bit 1—

config_sel

value of the input register.

(11)

• Bit 31:2—reserved.

Related Information

•

Altera Dual Configuration IP Core

(10)

You can only read the 12 most significant bit of the 29 bit user watchdog value using Dual Configuration

IP Core.

(11)

Reads the

config_sel

of the input register only. It will not reflect the physical CONFIG_SEL pin setting.

5-2

Altera Dual Configuration IP Core Avalon-MM Address Map

UG-M10CONFIG

2015.05.04

Altera Corporation

Altera Dual Configuration IP Core References