Unique chip id, Altera unique chip id ip core, Jtag secure mode – Altera MAX 10 FPGA User Manual

Page 20

Unique Chip ID

Unique chip ID provides the following features:

• Identifies your device in your design as part of a security feature to protect your design from an

unauthorized device.

• Provides non-volatile 64-bits unique ID for each MAX 10 device with write protection.

You can use the Altera Unique Chip ID IP core to acquire the chip ID of your MAX 10 device.

Related Information

•

on page 4-1

•

Altera Unique Chip ID IP Core Ports

Altera Unique Chip ID IP Core

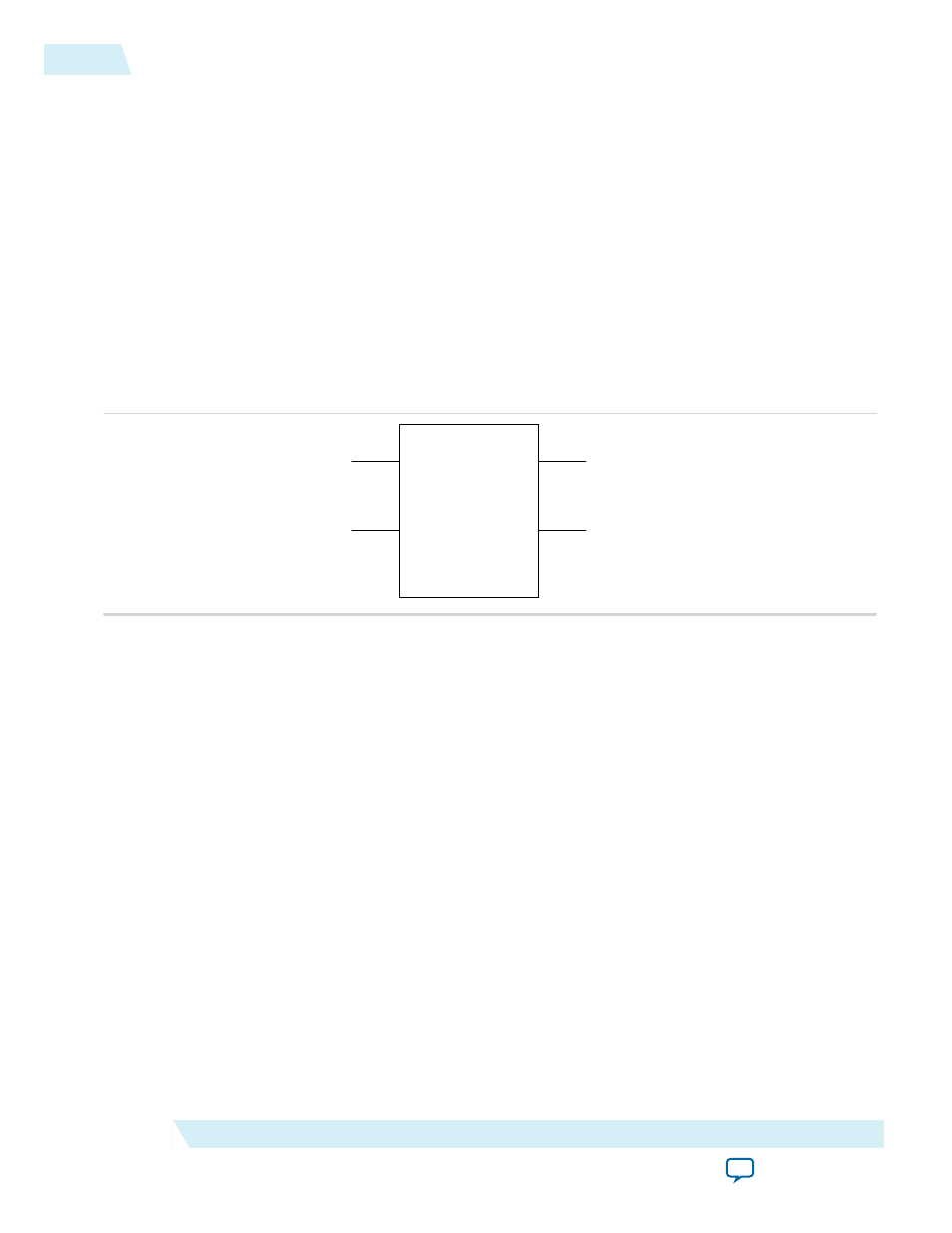

Figure 2-7: Altera Unique Chip ID IP Core Block Diagram

Altera Unique

Chip ID

clkin

data_valid

chip_id[63..0]

reset

At the initial state, the

data_valid

signal is low because no data is read from the unique chip ID block.

After feeding a clock signal to the

clkin

input port, the Altera Unique Chip ID IP core begins to acquire

the chip ID of your device through the unique chip ID block. After acquiring the chip ID of your device,

the Altera Unique Chip ID IP core asserts the

data_valid

signal to indicate that the chip ID value at the

output port is ready for retrieval.

The operation repeats only when you provide another clock signal when the

data_valid

signal is low. If

the

data_valid

signal is high when you provide another clock signal, the operation stops because the

chip_id[63..0]

output holds the chip ID of your device.

A minimum of 67 clock cycles are required for the

data_valid

signal to go high.

The

chip_id[63:0]

output port holds the value of chip ID of your device until you reconfigure the device

or reset the Altera Unique Chip ID IP core.

JTAG Secure Mode

In JTAG Secure mode, the device only allows mandatory JTAG 1149.1 instructions to be exercised.

You can enable the JTAG secure when generating the

.pof

in the

Convert Programming Files

. To exit JTAG

secure mode, issue the

UNLOCK

JTAG instruction. The

LOCK

JTAG instruction puts the device in the JTAG

secure mode again. The

LOCK

and

UNLOCK

JTAG instructions can only be issued through the JTAG core

access.

2-16

Unique Chip ID

UG-M10CONFIG

2015.05.04

Altera Corporation

MAX 10 FPGA Configuration Schemes and Features