Remote system upgrade circuitry input control – Altera MAX 10 FPGA User Manual

Page 15

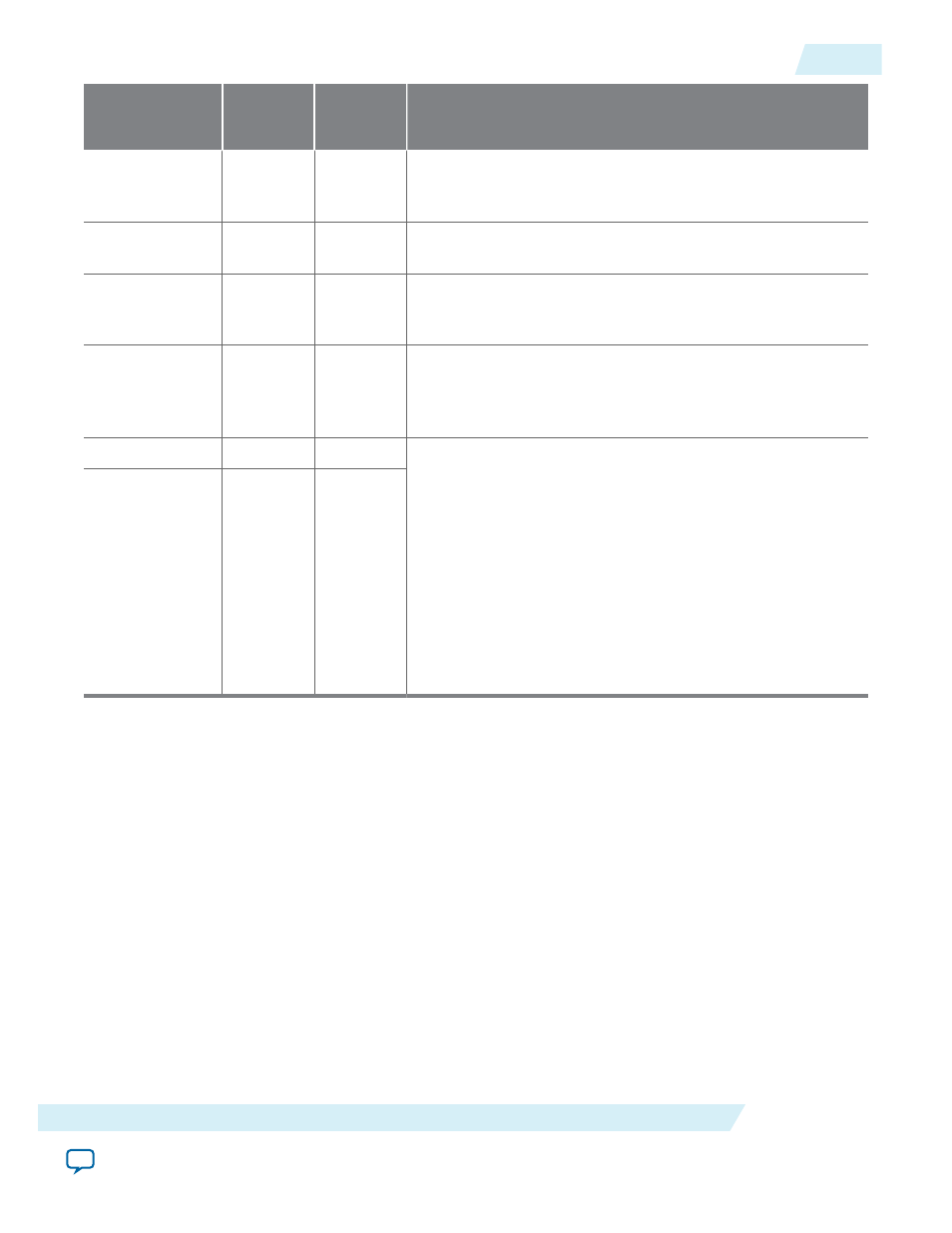

Core Signal Name

Logical

Signal

Name

Input/

Output

Description

RU_DOUT

regout

Output

Use this signal to get output data from the shift register. Data

is clocked out on each rising edge of

RU_CLK

if

RU_SHIFTnLD

is

asserted.

RU_nRSTIMER

rsttimer

Input

Use this signal to reset the user watchdog timer. A falling edge

of this signal triggers a reset of the user watchdog timer.

RU_nCONFIG

rconfig

Input

Use this signal to reconfigure the device. Driving this signal

low triggers the device to reconfigure if you enable the remote

system upgrade feature.

RU_CLK

clk

Input

The clock to the remote system upgrade circuitry. All registers

in this clock domain are enabled in user mode if you enable

the remote system upgrade. Shift register and input register

are positive edge flip-flops.

RU_SHIFTnLD

shiftnld

Input

Control signals that determine the mode of remote system

upgrade circuitry.

• When

RU_SHIFTnLD

is driven low and

RU_CAPTnUPDT

is

driven low, the input register is loaded with the contents of

the shift register on the rising edge of

RU_CLK

.

• When

RU_SHIFTnLD

is driven low and

RU_CAPTnUPDT

is

driven high, the shift register captures values from the

input_cs_ps module on the rising edge of

RU_CLK

.

• When

RU_SHIFTnLD

is driven high, the

RU_CAPTnUPDT

will

be ignored and the shift register shifts data on each rising

edge of

RU_CLK

.

RU_CAPTnUPDT

captnupdt

Input

Related Information

•

Accessing the Remote System Upgrade Block Through User Interface

Provides more information about accessing the remote system upgrade through user interface atom.

•

Provides more information about Remote System Upgrade timing specifications.

Remote System Upgrade Circuitry Input Control

The remote system upgrade circuitry has three modes of operation.

• Update—loads the values in the shift register into the input register.

• Capture—loads the shift register with data to be shifted out.

• Shift—shifts out data to the user logic.

UG-M10CONFIG

2015.05.04

Remote System Upgrade Circuitry Input Control

2-11

MAX 10 FPGA Configuration Schemes and Features

Altera Corporation