Altera MAX 10 FPGA User Manual

Page 10

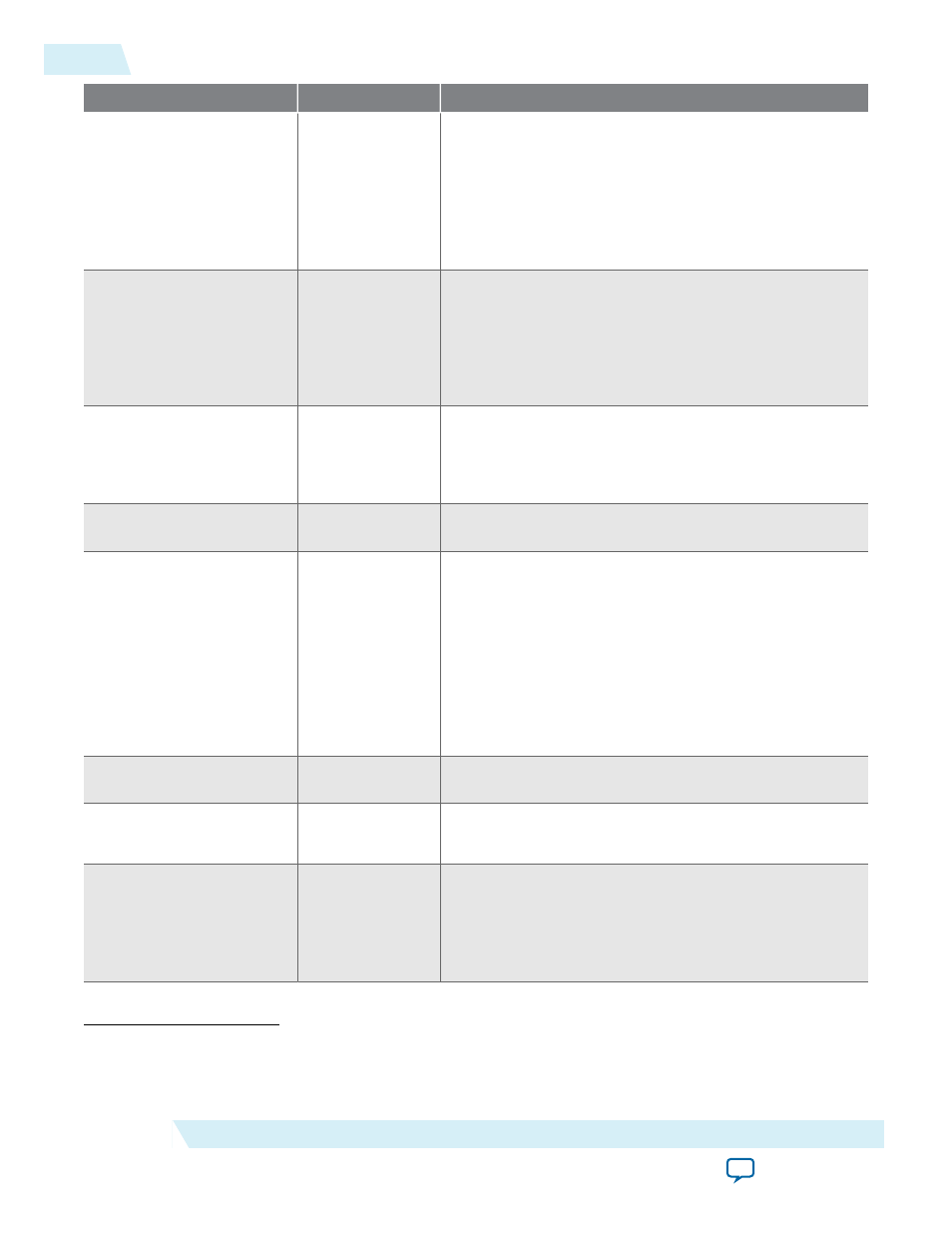

Instruction

Instruction Code

Description

ISC_ENABLE_HIZ

(1)

10 1100 1100

• Puts the device in ISP mode, tri-states all I/O pins,

and drives all core drivers, logic, and registers.

• Device remains in the ISP mode until the

ISC_

DISABLE

instruction is loaded and updated.

• The

ISC_ENABLE

instruction is a mandatory instruc‐

tion. This requirement is met by the

ISC_ENABLE_

CLAMP

or

ISC_ENABLE_HIZ

instruction.

ISC_ENABLE_CLAMP

(1)

10 0011 0011

• Puts the device in ISP mode and forces all I/O pins to

follow the contents of the JTAG boundary-scan

register.

• When this instruction is activated, all core drivers,

logics, and registers are frozen. The I/O pins remain

clamped until the device exits ISP mode successfully.

ISC_DISABLE

10 0000 0001

• Brings the device out of ISP mode.

• Successful completion of the

ISC_DISABLE

instruction

happens immediately after waiting 200 µs in the Run-

Test/Idle state.

ISC_PROGRAM

(2)

10 1111 0100

Sets the device up for in-system programming. Program‐

ming occurs in the run-test or idle state.

ISC_NOOP

(2)

10 0001 0000

• Sets the device to a no-operation mode without

leaving the ISP mode and targets the

ISC_Default

register.

• Use when:

• two or more ISP-compliant devices are being

accessed in ISP mode and;

• a subset of the devices perform some instructions

while other more complex devices are completing

extra steps in a given process.

ISC_ADDRESS_SHIFT

(2)

10 0000 0011

Sets the device up to load the flash address. It targets the

ISC_Address

register, which is the flash address register.

ISC_ERASE

(2)

10 1111 0010

• Sets the device up to erase the internal flash.

• Issue after

ISC_ADDRESS_SHIFT

instruction.

ISC_READ

(2)

10 0000 0101

• Sets the device up for verifying the internal flash

under normal user bias conditions.

• The

ISC_READ

instruction supports explicit

addressing and auto-increment, also known as the

Burst mode.

(1)

Do not issue the

ISC_ENABLE_HIZ

and

ISC_ENABLE_CLAMP

instructions from the core logic.

(2)

All ISP and real-time ISP instructions are disabled when the device is not in the ISP or real-time ISP mode,

except for the enabling and disabling instructions.

2-6

ISP and Real-Time ISP Instructions

UG-M10CONFIG

2015.05.04

Altera Corporation

MAX 10 FPGA Configuration Schemes and Features