Remote system upgrade status registers, Master state machine – Altera MAX 10 FPGA User Manual

Page 17

Bits

Name

Description

11:0

Reserved

Reserved—set to

0

.

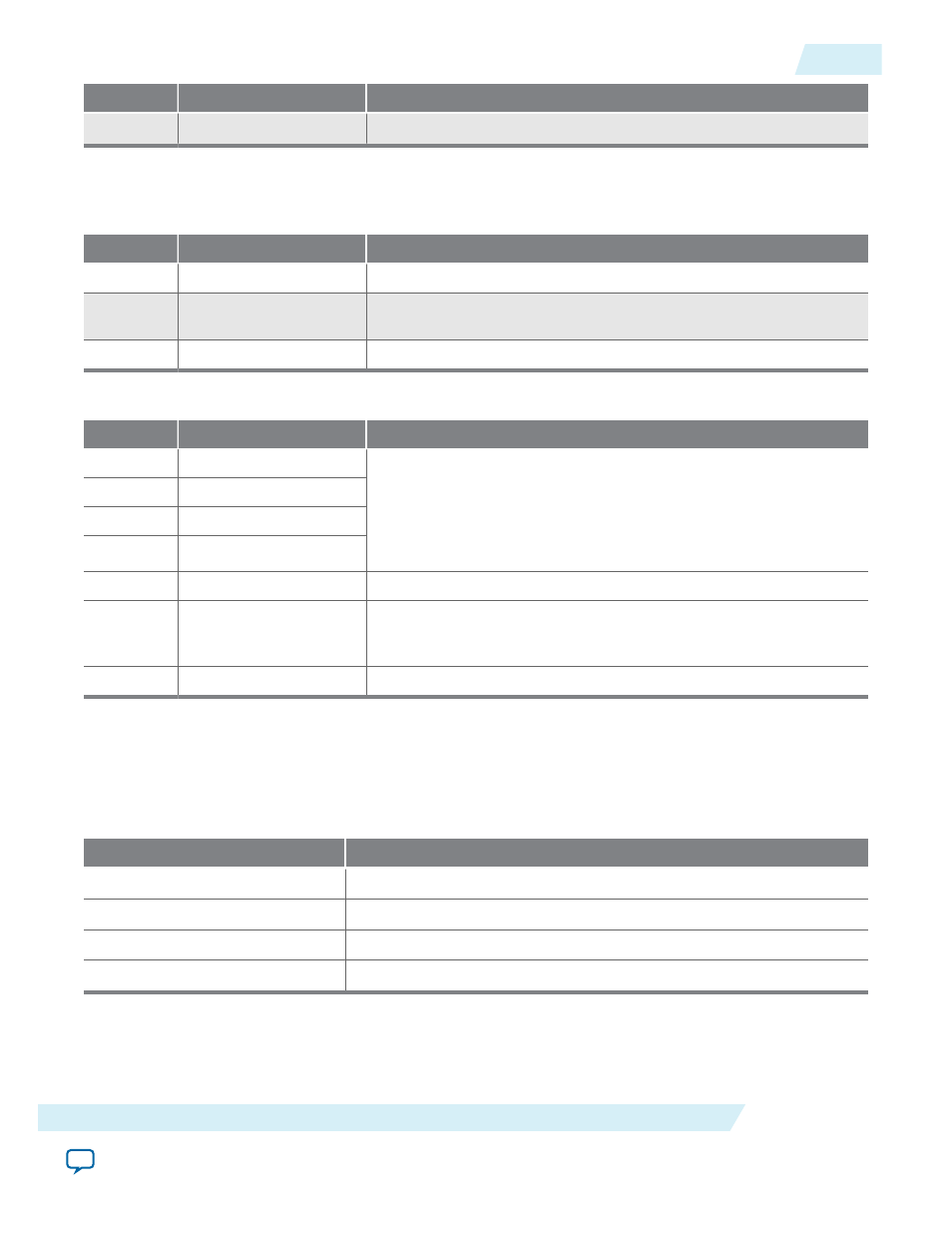

Remote System Upgrade Status Registers

Table 2-9: Remote System Upgrade Status Register—Current State Logic Bit for MAX 10 Devices

Bits

Name

Description

33:30

msm_cs

The current state of the master state machine (MSM).

29

ru_wd_en

The current state of the enabled user watchdog timer. The default

state is active high.

28:0

wd_timeout_value

The current, entire 29-bit watchdog time-out value.

Table 2-10: Remote System Upgrade Status Register—Previous State Bit for MAX 10 Devices

Bits

Name

Description

31

nconfig

An active high field that describes the reconfiguration sources

which caused the MAX 10 device to leave the previous application

configuration. In the event of a tie, the higher bit order takes

precedence. For example, if the

nconfig

and the

ru_nconfig

triggered at the same time, the

nconfig

takes precedence over the

ru_nconfig

.

30

crcerror

29

nstatus

28

wdtimer

27:26

Reserved

Reserved—set to

0

.

25:22

msm_cs

The state of the MSM when a reconfiguration event occurred. The

reconfiguration will cause the device to leave the previous applica‐

tion configuration.

21:0

Reserved

Reserved—set to

0

.

Master State Machine

The master state machine (MSM) tracks current configuration mode and enables the user watchdog

timer.

Table 2-11: Remote System Upgrade Master State Machine Current State Descriptions for MAX 10 Devices

msm_cs

Values

State Description

0010

Image 0 is being loaded.

0011

Image 1 is being loaded after a revert in application image happens.

0100

Image 1 is being loaded.

0101

Image 0 is being loaded after a revert in application image happens.

UG-M10CONFIG

2015.05.04

Remote System Upgrade Status Registers

2-13

MAX 10 FPGA Configuration Schemes and Features

Altera Corporation