Enabling dual-purpose pin, Enabling dual-purpose pin -2 – Altera MAX 10 FPGA User Manual

Page 32

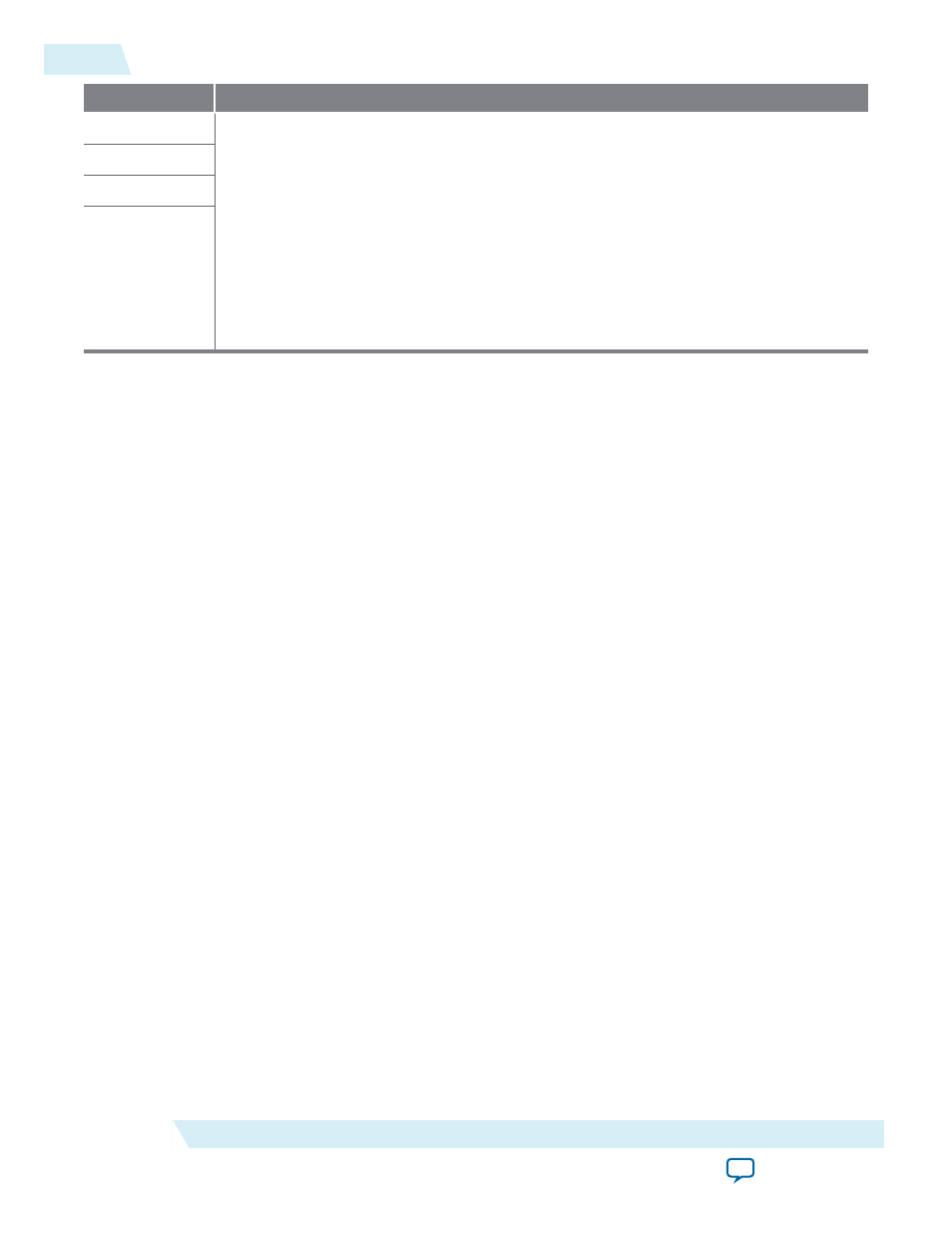

Pins

Guidelines

TDO

• If you intend to switch back and forth between user I/O pins and JTAG pin functions

using the JTAGEN pin, all JTAG pins must be assigned as single-ended I/O pins or

voltage-referenced I/O pins. Schmitt trigger input is the recommended input buffer.

• JTAG pins cannot perform as JTAG pins in user mode if you assign any of the JTAG

pin as a differential I/O pin.

• You must use the JTAG pins as dedicated pins and not as user I/O pins during JTAG

programming.

• Do not toggle JTAG pin during the initialization stage.

• Put the test access port (TAP) controller in reset state and drive the

TDI

and

TMS

pins

high and

TCK

pin low before the initialization.

TMS

TCK

TDI

Related Information

•

Provides more information about recommended resistor values.

•

•

Enabling Dual-purpose Pin

To use the configuration and JTAG pins as user I/O in user mode, you must do the following in the

Quartus II software:

1. On the Assignments menu, click Device.

2. Click Device and Pin Options.

3. Select the General tab of Device and Pin Options.

4. In the General Options list, do the following:

• Check the Enable JTAG pin sharing to use JTAG pins as user I/O.

• Uncheck the Enable nCONFIG, nSTATUS, and CONF_DONE pins to use configuration pins as

user I/O.

Related Information

•

•

Configuring MAX 10 Devices using JTAG Configuration

The Quartus II software generates a .sof that can used for JTAG configuration. You can directly configure

the MAX 10 device by using a download cable with the Quartus II software programmer.

Alternatively, you can use the JRunner software with a JAM Standard Test and Programming Language

(STAPL) Format File (.jam) or JAM Byte Code File (.jbc) with other third-party programmer tools.

Related Information

•

3-2

Enabling Dual-purpose Pin

UG-M10CONFIG

2015.05.04

Altera Corporation

MAX 10 FPGA Configuration Design Guidelines