Reset, Configuration, Configuration error handling – Altera MAX 10 FPGA User Manual

Page 29: Initialization, User mode, Max 10 configuration pins, Max 10 configuration pins -25

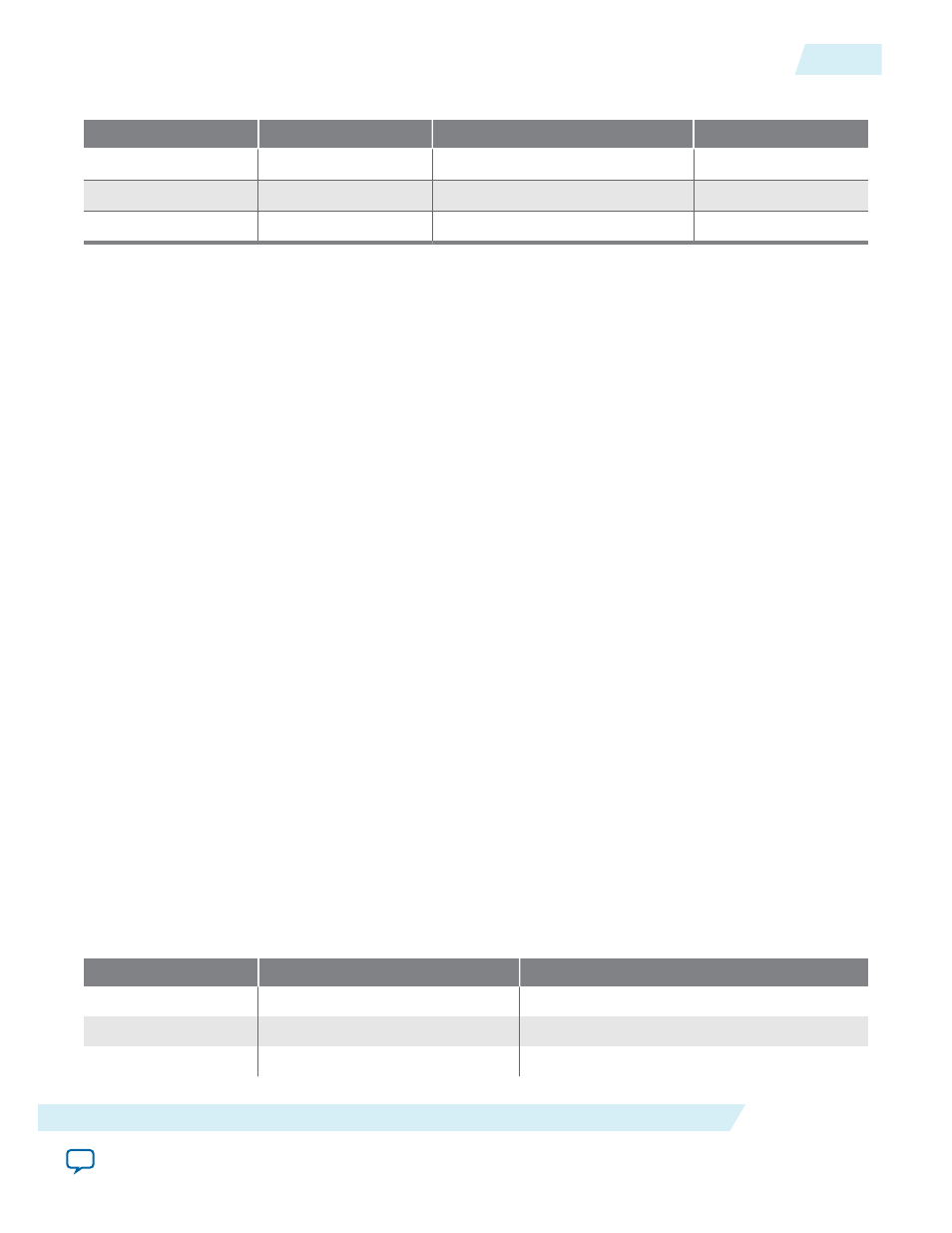

Table 2-21: POR Requirements and Timing for MAX 10 Devices

Instant-On

POR Delay Setting

Ramp Rate Requirement (t

RAMP

)

POR Delay (t

POR

)

Enabled

Don’t Care

200 us to 3 ms

No delay

Disabled

Fast POR

200 us to 3 ms

3 ms to 9 ms

Disabled

Standard POR

200 us to 50 ms

50 ms to 200 ms

Reset

POR delay is the time frame between the time when all the power supplies monitored by the POR

circuitry reach the recommended operating voltage and when

nSTATUS

is released high and the MAX 10

device is ready to begin configuration.

Configuration

During configuration, the configuration data is written to the device.

Configuration Error Handling

To restart configuration automatically, turn on the Auto-restart configuration after error option in the

General page of the Device and Pin Options dialog box in the Quartus II software.

If you do not turn on this option, you can monitor the

nSTATUS

pin to detect errors. To restart configura‐

tion, pull the

nCONFIG

pin low for at least the duration of t

CFG

.

Initialization

After you pull the

CONF_DONE

pin high, the initialization sequence begins. The initialization clock source is

from the internal oscillator. By default, the internal oscillator is the clock source for initialization. If you

use the internal oscillator, the MAX 10 device will receive enough clock cycles for proper initialization.

User Mode

After the initialization completes, your design starts executing. The user I/O pins will then function as

specified by your design.

MAX 10 Configuration Pins

All configuration pins and JTAG pins in MAX 10 devices are dual-purpose pins. The configuration pins

function as configuration pins prior to user mode. When the device is in user mode, they function as user

I/O pins or remain as configuration pins.

Table 2-22: Configuration Pin Summary for MAX 10 Devices

All pins are powered by V

CCIO

Bank 1B and 8.

Configuration Pin

Input/Output

Configuration Scheme

CRC_ERROR

Output only, open-drain

Optional, JTAG and internal configurations

CONFIG_SEL

Input only

Internal configuration

DEV_CLRn

Input only

Optional, JTAG and internal configurations

UG-M10CONFIG

2015.05.04

Reset

2-25

MAX 10 FPGA Configuration Schemes and Features

Altera Corporation