Rockwell Automation 1746-HSCE,D17466.5 High-Speed Counter Module User Manual

Page 99

Publication 1746-UM006B-EN-P - August 2005

Configuration and Programming 4-39

I:e.0 Bit 4 - Rate Counter Overflow

When this bit is set, a Rate Period Counter overflow has been

detected. The bit is dynamically updated after every Rate Period. You

can adjust the Rate Period when an overflow is detected. When the

overflow occurs, the Rate Period will be set to ±32767. Refer to Rate

Counter Overflow in Chapter 5.

The module sets this bit to 1 when the Rate Period Counter

Overflows. This bit is cleared upon the 0 to 1 transition of the

Function Control bit.

I:e.0 Bit 5 - Rate Measure Overflow

When this bit is set to 1, one of the following conditions exist:

•

The calculated Rate Measurement input parameter exceeds the

maximum rate of ± 32767.

•

A Rate Period Counter overflow is detected.

The bit is dynamically updated after every Rate Measurement. When

the overflow occurs, the Rate Period will be set to ±32767 Hz.

When a Rate Period does not cause any overflows, the bit is cleared.

This bit is cleared upon the 0 to 1 transition of the Function Control

bit.

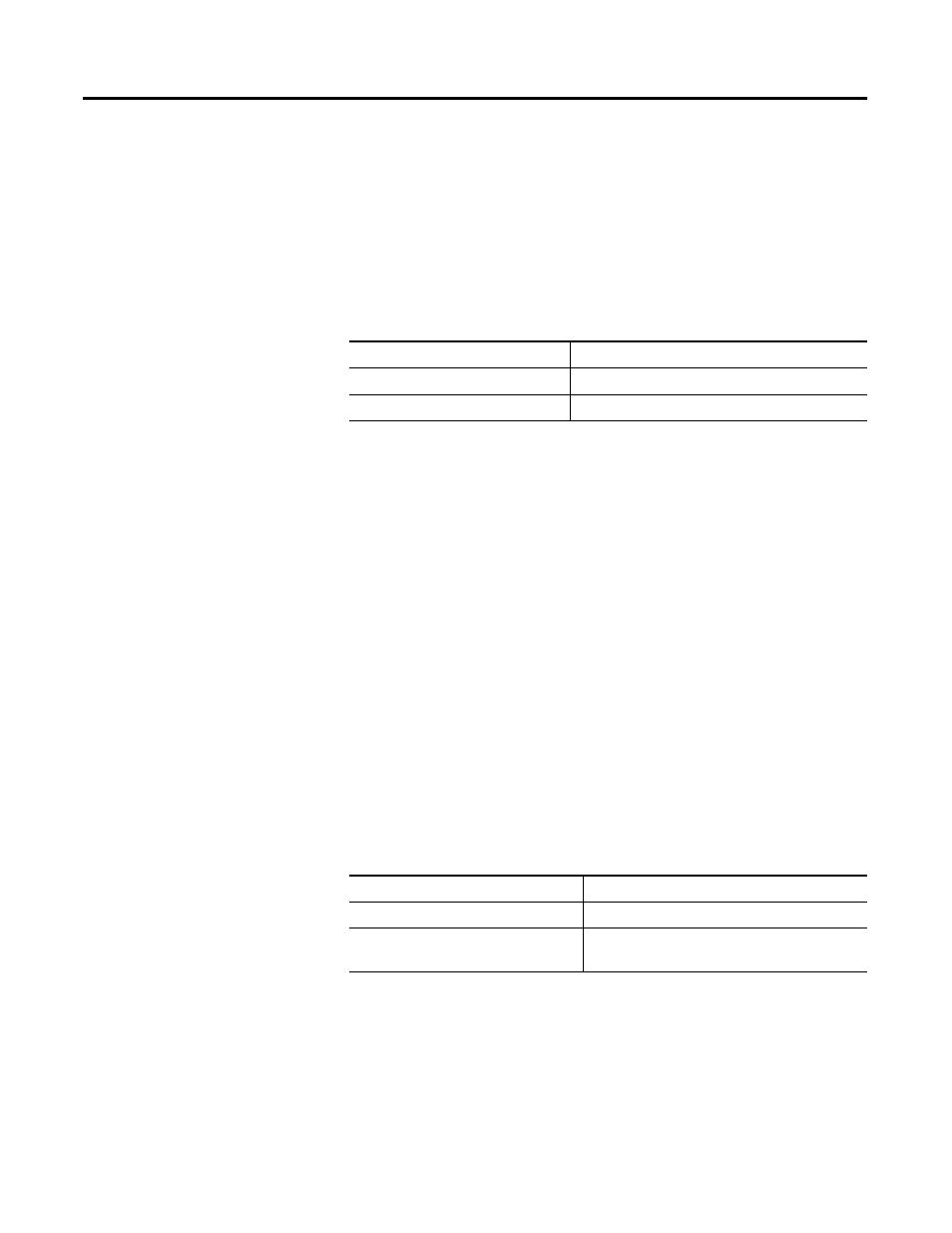

Rate Counter Overflow (bit 4)

Cause

0

No rate period overflow detected

1

Rate period counter overflow detected

Rate Measurement Overflow (bit 5)

Cause

0

No rate period overflow detected

1

Rate period counter overflow detected, or

maximum rate of ±32767 Hz has been met