Rockwell Automation 1746-HSCE,D17466.5 High-Speed Counter Module User Manual

Page 78

Publication 1746-UM006B-EN-P - August 2005

4-18 Configuration and Programming

I:e.0 Bit 5 - Rate Measurement Overflow

When this bit is set to 1, one of the following conditions exist:

•

The calculated Rate Measurement input parameter exceeds the

maximum rate of ± 32767 Hz.

•

A Rate Period Counter overflow is detected.

The bit is dynamically updated after every Rate Measurement. When

the overflow occurs, the Rate Period will be set to ±32767 Hz. The

module will continue to run the rate measurement calculation and will

clear the error if the input frequency drops below 32767 Hz. If

operating in the Rate Mode, the module controlled outputs are reset to

0 while this error is present. Outputs controlled from the user program

are not affected.

When a Rate Period does not cause any overflows, the bit is cleared.

This bit is cleared upon the 0 to 1 transition of the Function Control

bit.

I:e.0 Bits 6 through 9

Bits 6 through 9 are reserved and must be reset to 0.

I:e.0 Bit 10 - Critical Error

This bit is set (to 1) by the module whenever a Critical Error is

detected. It causes the module operation to halt (even though the

Function Control bit is set to 1) and module controlled outputs are

turned OFF.

The Critical Errors are:

•

Module Configuration Errors (fault LED flashes)

•

Linear Counter Overflow/Underflow (fault LED remains off)

For more information, refer to Error Handling in Chapter 5.

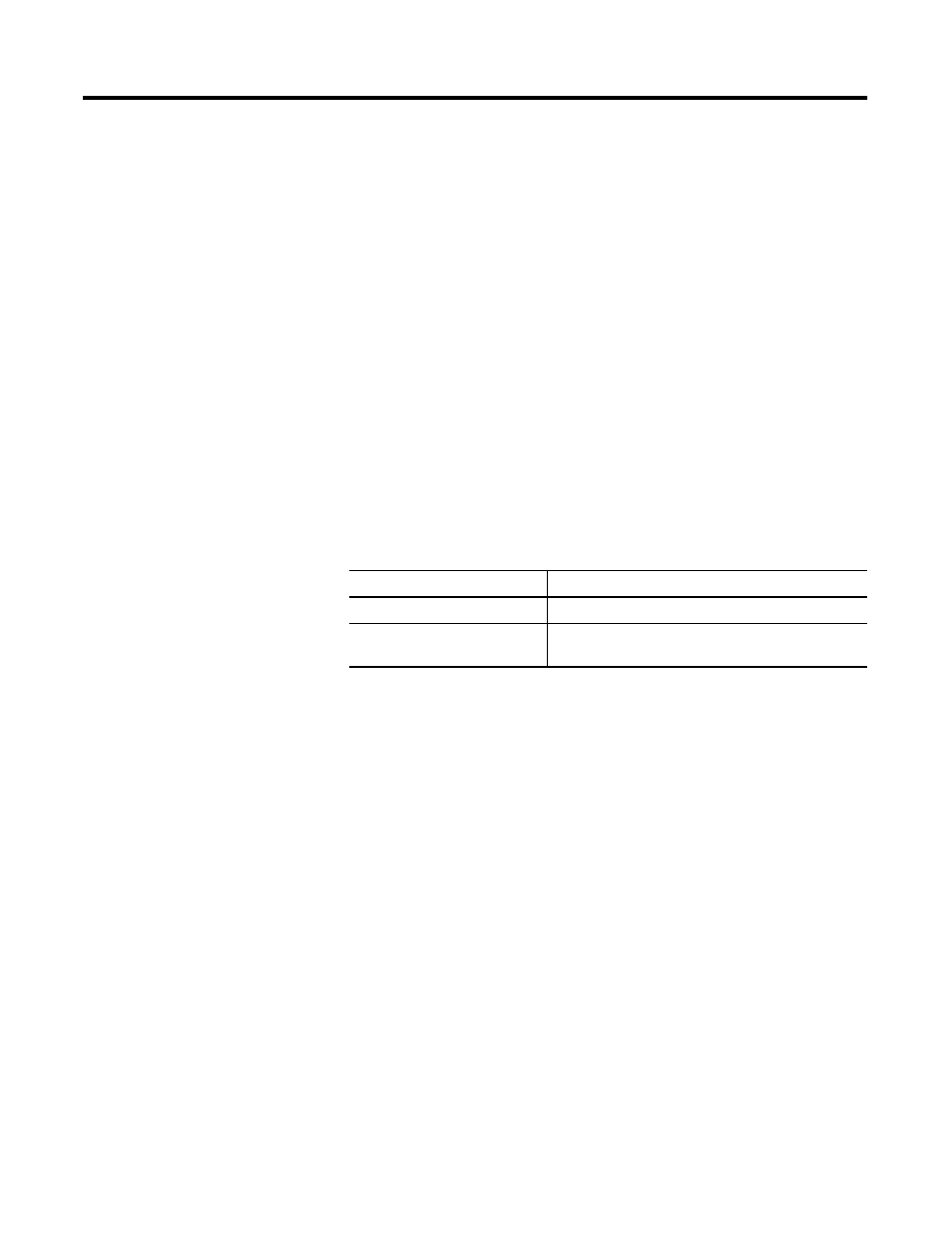

Rate Counter Overflow (bit 5)

Cause

0

No Rate Period overflow detected

1

Rate Period Counter overflow detected, or maximum

rate of ±32767 Hz has been met