Counter hold control, Counter hold control -10 – Rockwell Automation 1746-HSCE,D17466.5 High-Speed Counter Module User Manual

Page 28

Publication 1746-UM006B-EN-P - August 2005

2-10 Module Operation

The reset of the counter is edge triggered. It occurs only when all of

the conditions specified become true. If multiple conditions are

selected, the counter is reset on the last event’s 0 to 1 transition. For

example, if Z and LS are selected (011), Z by itself will not trigger the

reset. Z and LS must both be ON.

Counter Hold Control

The pulse counter value is held when the user program sets the

Counter Hold bit (M0:e.1/2) to 1. When this bit is set, the Accumulated

Count does not change when input pulses occur. However, the

counter reset is still active. The pulse counter’s Accumulated Count is

reset when a reset is received while the counter is held (Counter Hold

=1).

Counter Hold - bit 2

IMPORTANT

The time it takes for the counter to reset depends

upon the value it resets to. If the reset value is zero,

the counter resets immediately on the false to true

edge of the reset condition without losing subsequent

counts. If the reset value is nonzero, there is a delay

of up to 500 µs before the reset value is loaded.

Count pulses can be lost if they happen during the

delay time. Refer to Timing Information in Appendix

A.

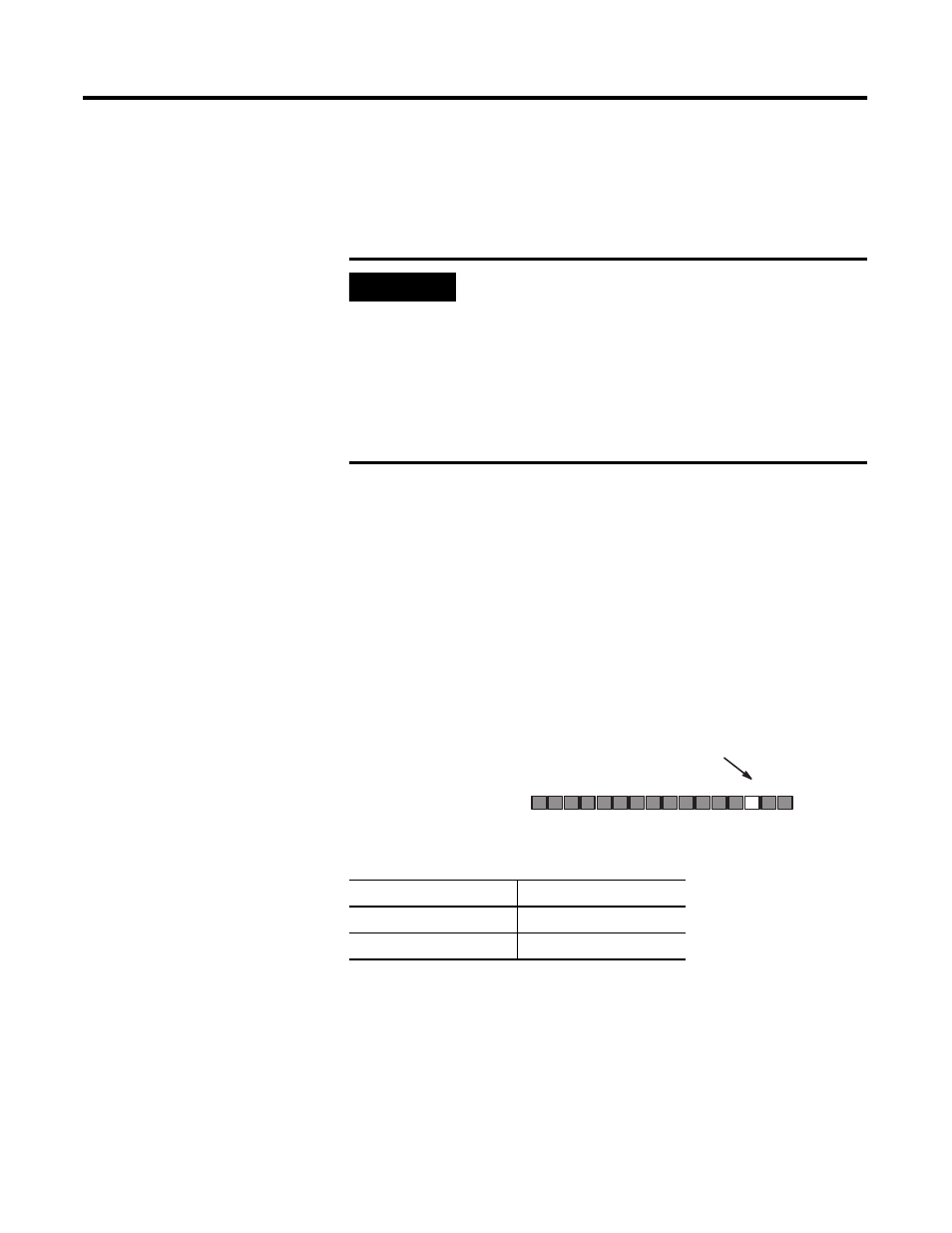

Counter Hold (bit 2)

Counter State

0

counter is running

1

count is held

Setup and Control Word, Word 1

Bit Number (decimal)

Counter Hold

15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

M0:e.1