Agilent Technologies HDMP-3001 User Manual

Page 97

97

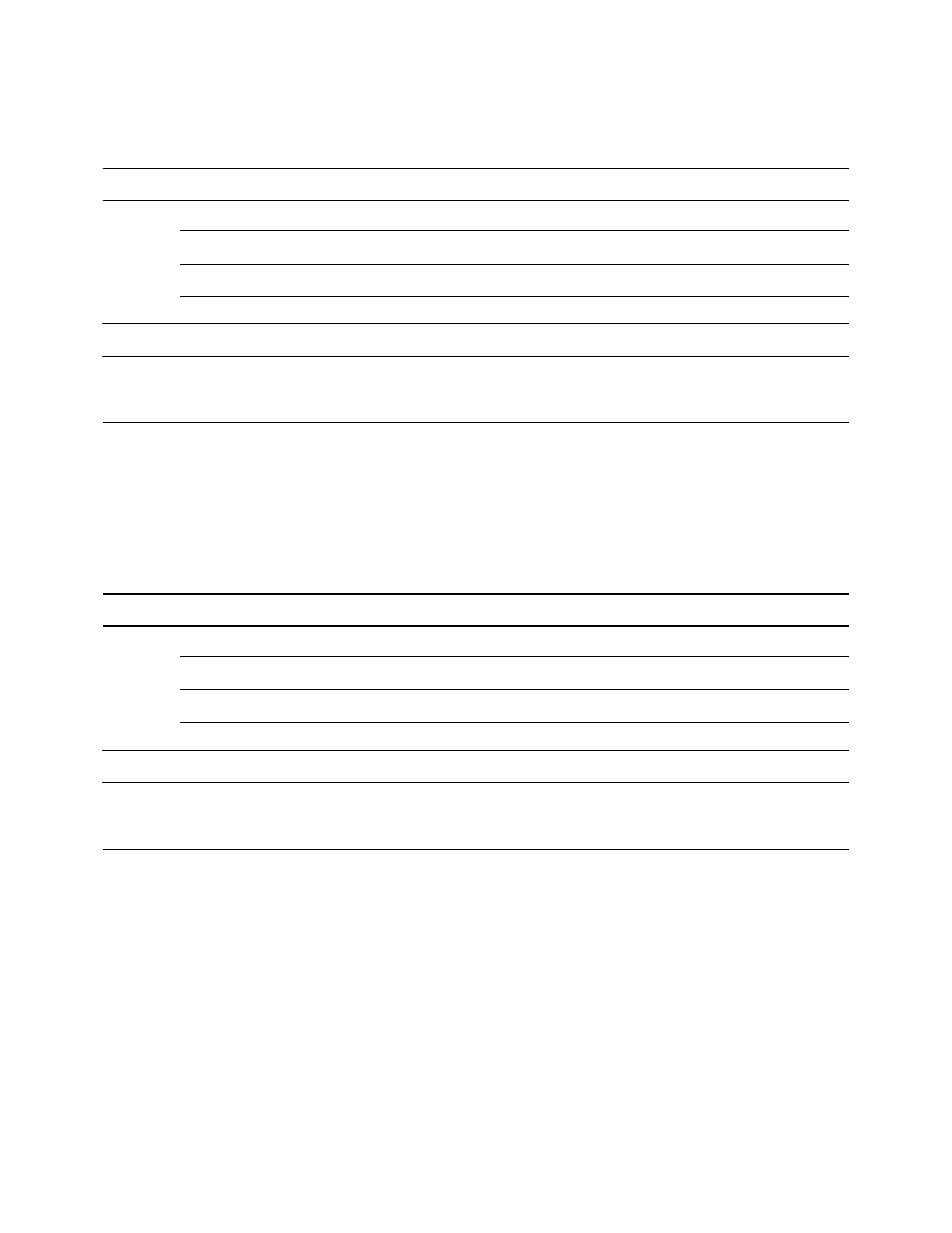

ADDR = 0x1D4-7: Receive MII Frames Transmitted OK

ADDR

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Bit name

0x1D4

RX_MII_FRAMES_XMIT_OK [7:0]

0x1D5

RX_MII_FRAMES_XMIT_OK [15:8]

0x1D6

RX_MII_FRAMES_XMIT_OK [23:16]

0x1D7

Fixed 0

R/W

RO

Value

0

after

reset

RX_MII_FRAMES_XMIT_OK

is the RX MII Frames Transmitted OK counter. It is non-resetable except

that a hard or soft reset will clear it. After reaching its max value the counter starts over from zero again.

This counter is incremented by each complete frame that is transmitted on the MII interface without

RX_ER being asserted. That is, it is incremented by each frame that did not increment any one of the error

counters.

ADDR = 0x1D8-B: Receive FCS and HEC Error Counter

ADDR

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Bit name

0x1D8

RX_FCS_HEC_ERR [7:0]

0x1D9

RX_FCS_HEC_ERR [15:8]

0x1DA

RX_FCS_HEC_ERR [23:16]

0x1DB

Fixed 0

R/W

RO

Value

0

after

reset

RX_FCS_HEC_ERR

is the RX FCS and HEC Error counter. It is non-resetable except that a hard or soft

reset will clear it. After reaching its max value the counter starts over from zero again.

This counter is incremented by each frame that did not increment any of the RX_FIFO_UR_ERR,

RX_FIFO_OF_ERR, RX_MIN_ERR or RX_MAX_ERR counters, but was received with an FCS or HEC error

(and checking was enabled) or contained an unrecognized LAPS control flag.