Agilent Technologies HDMP-3001 User Manual

Page 100

100

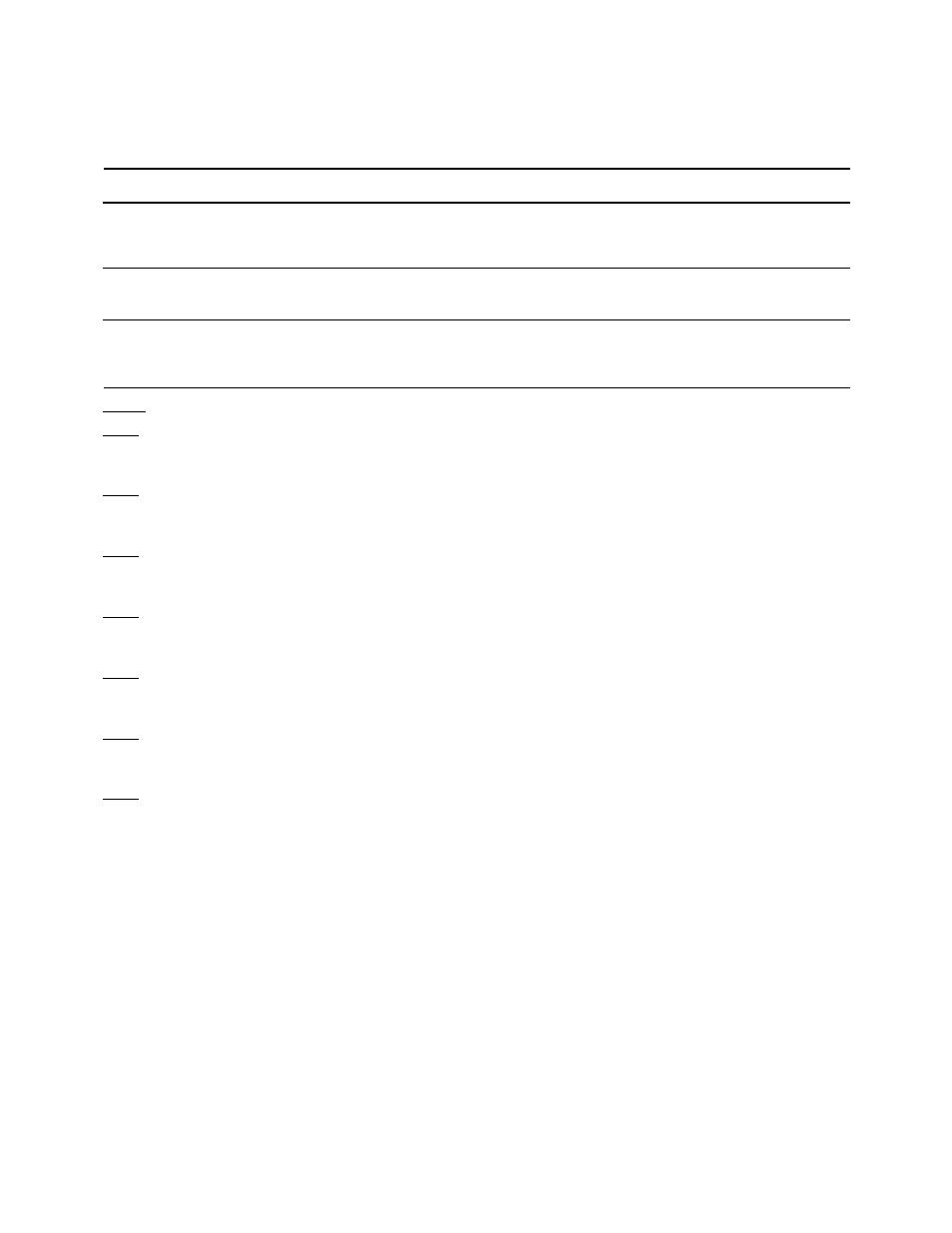

ADDR = 0x1EC: Ethernet Receive Interrupt Event

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Bit name Reserved

NEW_RX_ NEW_RX_ NEW_RX_

NEW_RX_

NEW_RX_

NEW_RX_

NEW_RX_

MIN_ERR

MAX_ERR OOS_ERR

FORM_

FIFO_UR_

FIFO_OF_

FCS_HEC_

DEST_ERR

ERR

ERR

ERR

R/W

—

R/W

R/W

R/W

R/W

R/W

R/W

R/W

W1C

W1C

W1C

W1C

W1C

W1C

W1C

Value

0

0

0

0

0

0

0

0

after

reset

Bits 7:

Reserved

Bit 6:

NEW_RX_MIN_ERR

is set whenever a new RX min frame size error occurs and cleared when a

one is written to this bit. For more information, refer to the register definition of the RX_MIN_ERR

counter.

Bit 5:

NEW_RX_MAX_ERR

is set whenever a new RX max frame size error occurs and cleared when a

one is written to this bit. For more information, refer to the register definition of the

RX_MAX_ERR counter.

Bit 4:

NEW_RX_OOS_ERR

is set whenever a new RX Out of Sync Error occurs and cleared when a one

is written to this bit. For more information, refer to the register definition of RX Out of Sync Error

counter.

Bit 3:

NEW_RX_FORM_DEST_ERR

is set whenever a new RX Format/Destination Error occurs and

cleared when a one is written to this bit. For more information, refer to the register definition of

RX Format/Destination Error counter.

Bit 2:

NEW_RX_FIFO_UR_ERR

is set whenever a new RX FIFO Underrun Error occurs and cleared

when a one is written to this bit. For more information, refer to the register definition of RX FIFO

Underrun Error counter.

Bit 1:

NEW_RX_FIFO_OF_ERR

is set whenever a new RX FIFO Overflow Error occurs and cleared

when a one is written to this bit. For more information, refer to the register definition of RX FIFO

Overflow Error counter.

Bit 0:

NEW_RX_FCS_HEC_ERR

is set whenever a new RX FCS and HEC Error occurs and cleared

when a one is written to this bit. For more information, refer to the register definition of RX FCS

and HEC Error counter.