Agilent Technologies HDMP-3001 User Manual

Page 56

56

This is a BIP calculating control register.

Bits 7-3: Reserved

Bit 2:

TX_B1_INV

is set to calculate B1 by odd parity (for testing purposes).

Bit 1:

TX_B2_INV

is set to calculate B2 by odd parity (for testing purposes).

Bit 0:

TX_B3_INV

is set to calculate B3 by odd parity (for testing purposes).

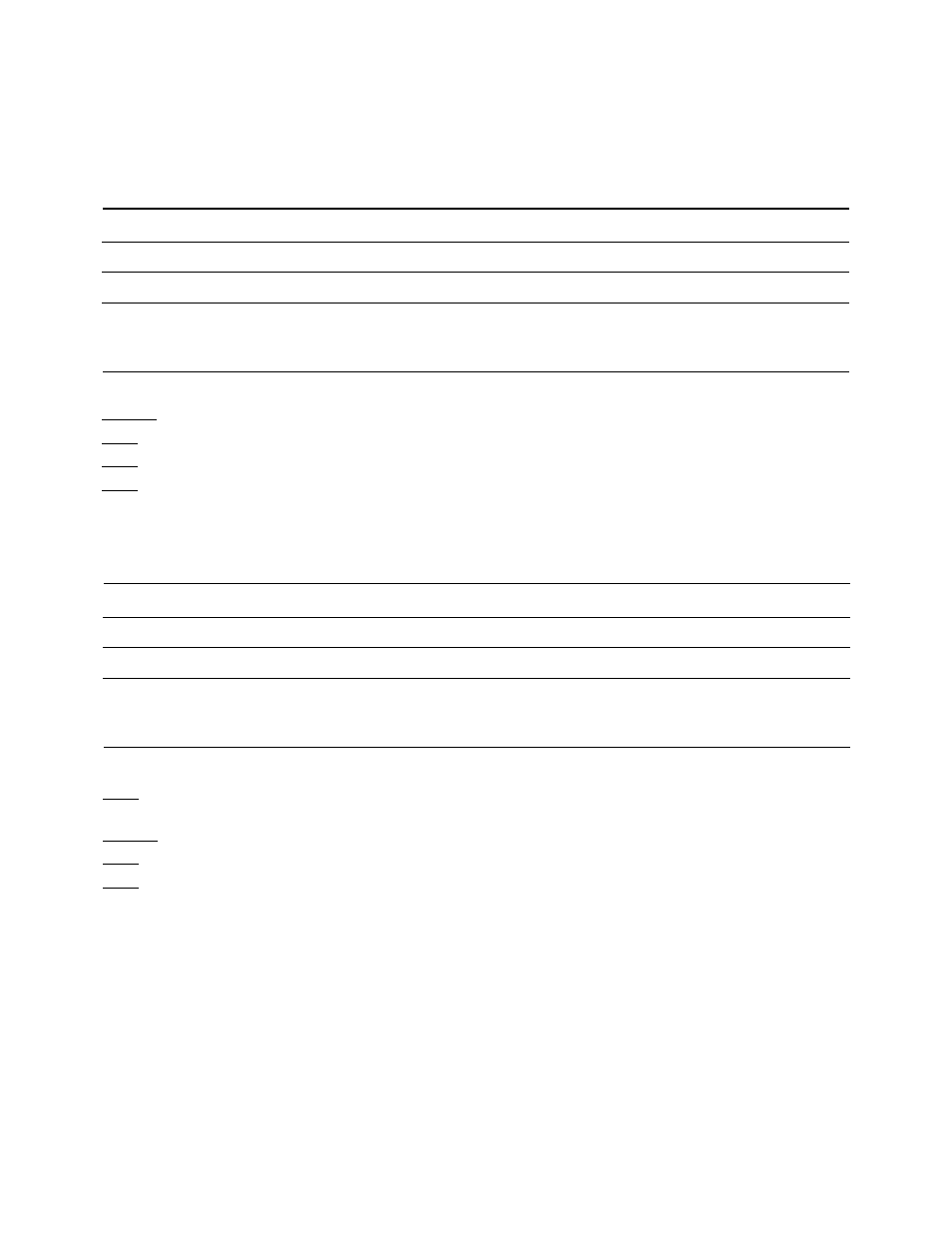

5.3 SONET/SDH Transmit Registers

ADDR=0x09C: Transmit BIP control

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Bit name Reserved

Reserved

Reserved

Reserved

Reserved

TX_B1_INV

TX_B2_INV

TX_B3_INV

R/W

—

—

—

—

—

R/W

R/W

R/W

Value

0

0

0

0

0

0

0

0

after

reset

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Bit name TX_LAIS

Reserved

Reserved

Reserved

Reserved

Reserved

LRDI_INH

LREI_INH

R/W

R/W

—

—

—

—

—

R/W

R/W

Value

0

0

0

0

0

0

0

0

after

reset

This is a Transmit AIS, RDI, REI Control register.

Bit 7:

TX_LAIS

is set to generate all ones to the entire SONET/SDH payload except for the first 3 rows

of Section Overhead.

Bits 6-2: Reserved

Bit 1:

LRDI_INH

is set to disable automatic generation of Line Remote Defect Indication.

Bit 0:

LREI_INH

is set to disable automatic generation of Line Remote Error Indication.

ADDR=0x09D: Transmit AIS, RDI, REI Control