Agilent Technologies HDMP-3001 User Manual

Page 86

86

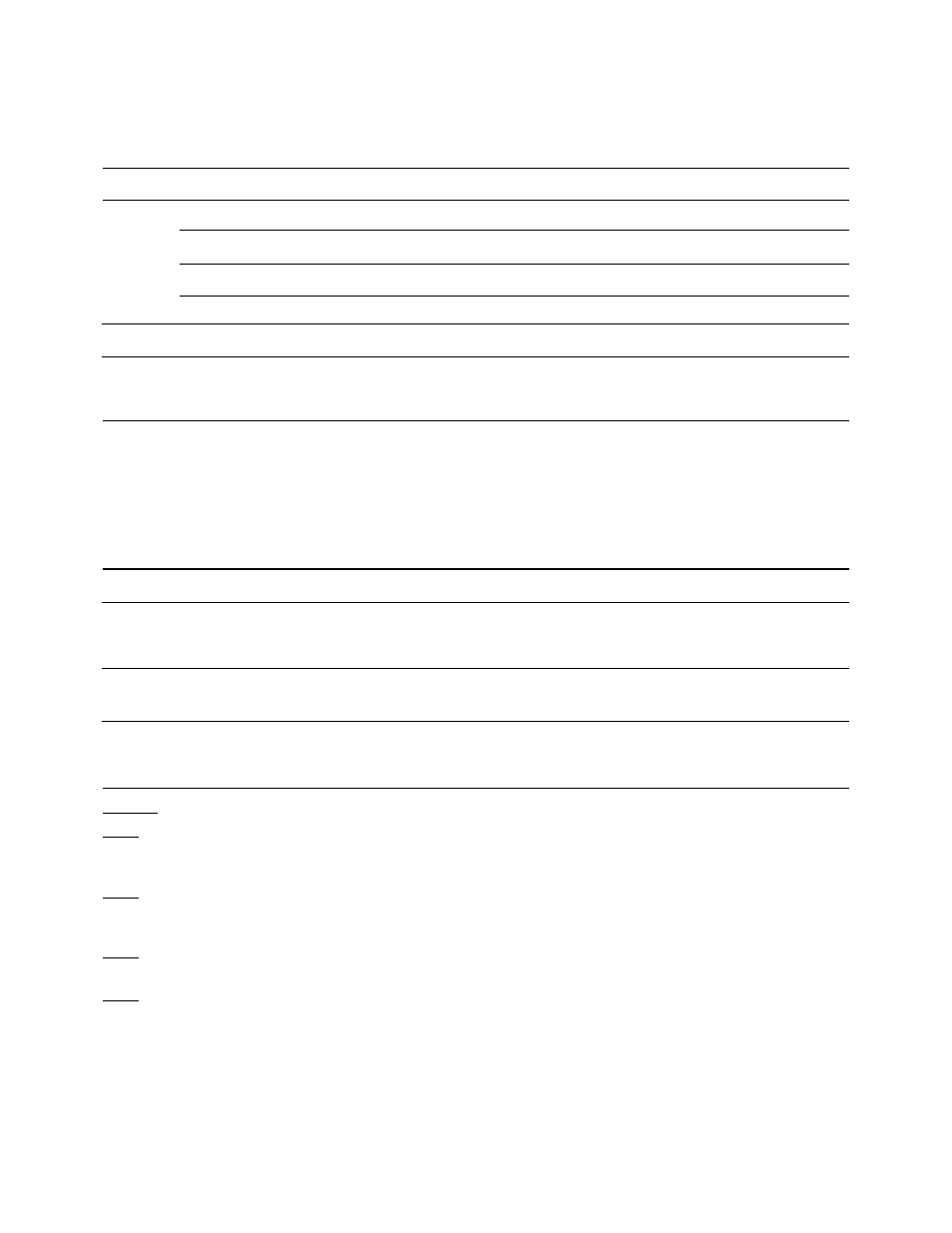

ADDR = 0x19C-F: TX FIFO Underrun Error

ADDR

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Bit name

0x19C

TX_FIFO_UR_ERR [7:0]

0x19D

TX_FIFO_UR_ERR [15:8]

0x19E

Fixed 0

0x19F

Fixed 0

R/W

RO

Value

0

after

reset

TX_FIFO_UR_ERR

is the TX_FIFO Underrun Error counter. It is non-resetable except that a hard or soft

reset will clear it. After reaching its max value the counter starts over from zero again.

This counter is incremented each time there is a FIFO underrun and hence a frame is discarded.

ADDR = 0x1A0: Ethernet Transmit Interrupt Event

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Bit name Reserved

Reserved

Reserved

Reserved

NEW_TX_

NEW_TX_

NEW_TX_

NEW_TX_

FIFO_UR_

FIFO_OF_

ER_ERR

MII_ALIGN

ERR

ERR

_ERR

R/W

—

—

—

—

R/W

R/W

R/W

R/W

W1C

W1C

W1C

W1C

Value

0

0

0

0

0

0

0

0

after

reset

Bits 7-4: Reserved

Bit 3:

NEW_TX_FIFO_UR_ERR

is set whenever a new TX FIFO Underrun Error occurs and is cleared

when a 1 is written to this bit. For more information, refer to the register definition of TX FIFO

Underrun Error counter.

Bit 2:

NEW_TX_FIFO_OF_ERR

is set whenever a new TX FIFO Overflow Error occurs and cleared

when a 1 is written to this bit. For more information, refer to the register definition of TX FIFO

Overflow Error counter.

Bit 1:

NEW_TX_ER_ERR

is set whenever a new TX_ER Error occurs and cleared when a 1 is written

to this bit. For more information, refer to the register definition of TX_ER Error counter.

Bit 0:

NEW_TX_MII_ALIGN_ERR

is set whenever a new TX MII Alignment Error occurs and cleared

when a 1 is written to this bit. For more information, refer to the register definition of TX MII

Alignment Error counter.