Agilent Technologies HDMP-3001 User Manual

Page 6

6

•

Implemented in 0.25 micron

CMOS with 1.8 V core, 3.3 V I/O

power and LVCMOS

compatible I/Os.

•

Provides a 16-bit general pur-

pose I/O (GPIO) register.

•

Device power-up initialization

optionally through 2-wire

EEPROM interface.

•

Configurable by hardware to

be connected to either a PHY

or a MAC from the system

connectivity viewpoint.

1.3 Applications

•

Multi-Service Ethernet

Switches.

•

Enhanced Services SONET/

SDH Add/Drop Multiplexers

(ADMs).

•

DSU/CSUs.

1.4 Benefits

•

Allows LANs to be intercon-

nected over leased OC-3c

lines, thereby extending a LAN

to multiple sites.

•

Ethernet switches in each LAN

can be connected together di-

rectly which reduces cost and

complexity.

•

Enables Transparent LAN

Services which, unlike POS

solutions, do not require

WAN access routers.

1.5 Interfaces

•

System interface is a 25 MHz

IEEE 802.3 full-duplex, 100

Mb/s Ethernet MII port that

connects to either a PHY or a

MAC.

•

Line side SERDES interface is

8-bit parallel data operating at

19.44 MHz. SONET/SDH

framer is compliant to

specifications ANSI T1.105 and

ITU G.707.

•

Serial data channels for add

and drop of SONET overhead

bytes E1, E2, F1 and DCC.

•

8-bit microprocessor

interface allows direct

connection to the Motorola

MPC860.

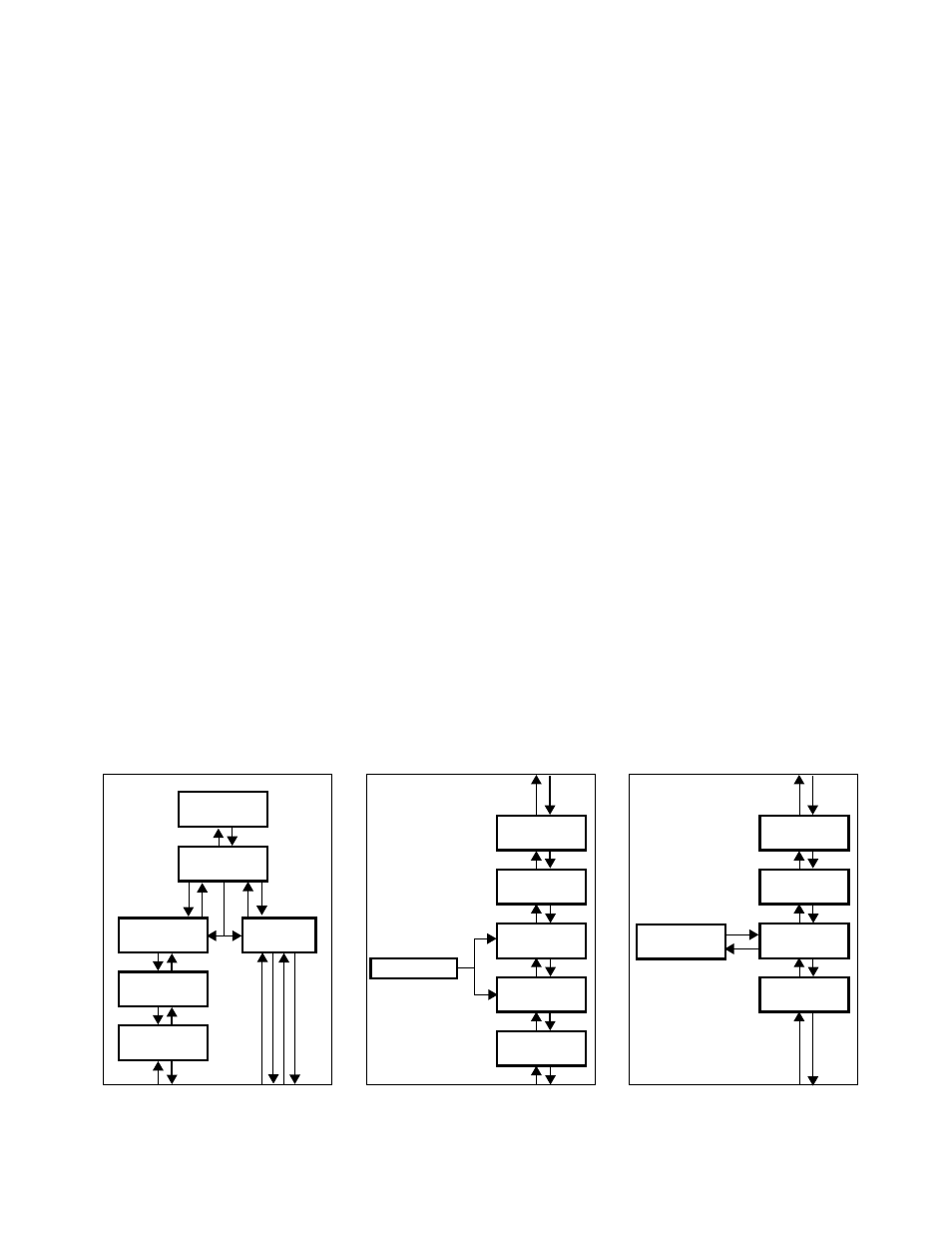

AGILENT

FIBER OPTICS

SERDES

WITH CDR

AGILENT

HDMP-3001

SWITCH

FABRIC

MICROPROCESSOR

ETHERNET

PHYs

MDIO BUS

OC-3c PORT

ETHERNET PORTS

PORT ON ETHERNET SWITCH

LINE CARD OF SONET ADM

ETHERNET

PHY

AGILENT

HDMP-3001

ADM

EEPROM

SERDES

WITH CDR

AGILENT

FIBER OPTICS

DROP SIDE - 100 MBIT/S

FULL-DUPLEX ETHERNET

OC-48/12

SONET RING

MICROPROCESSOR

STAND ALONE DSU/CSU

ETHERNET

PHY

AGILENT

HDMP-3001

SONET SERDES

WITH CDR

AGILENT

FIBER OPTICS

100 MBIT/S

FULL-DUPLEX ETHERNET

OC-3c

Figure 2. HDMP-3001 Applications

•

IEEE 802.3 MDIO management

interface.

•

Standard 2-wire EEPROM

interface for optional boot-up

configuration.

•

Provides 16-bit General

Purpose I/O (GPIO) register.

•

Provides standard five-pin

IEEE 1149.1 JTAG test port.

1.6 Data Processing

•

Complies to the GFP (Generic

Framing Procedure) draft

specification, revision 2, of

ANSI T1X1.5 and implements

both the null and linear header

options.

•

Complies to the LAPS (Link

Access Procedure – SDH)

specification X.86 of ITU.

•

Optional self-synchronous

X

43

+1 scrambling of the

payload.