Agilent Technologies HDMP-3001 User Manual

Page 49

49

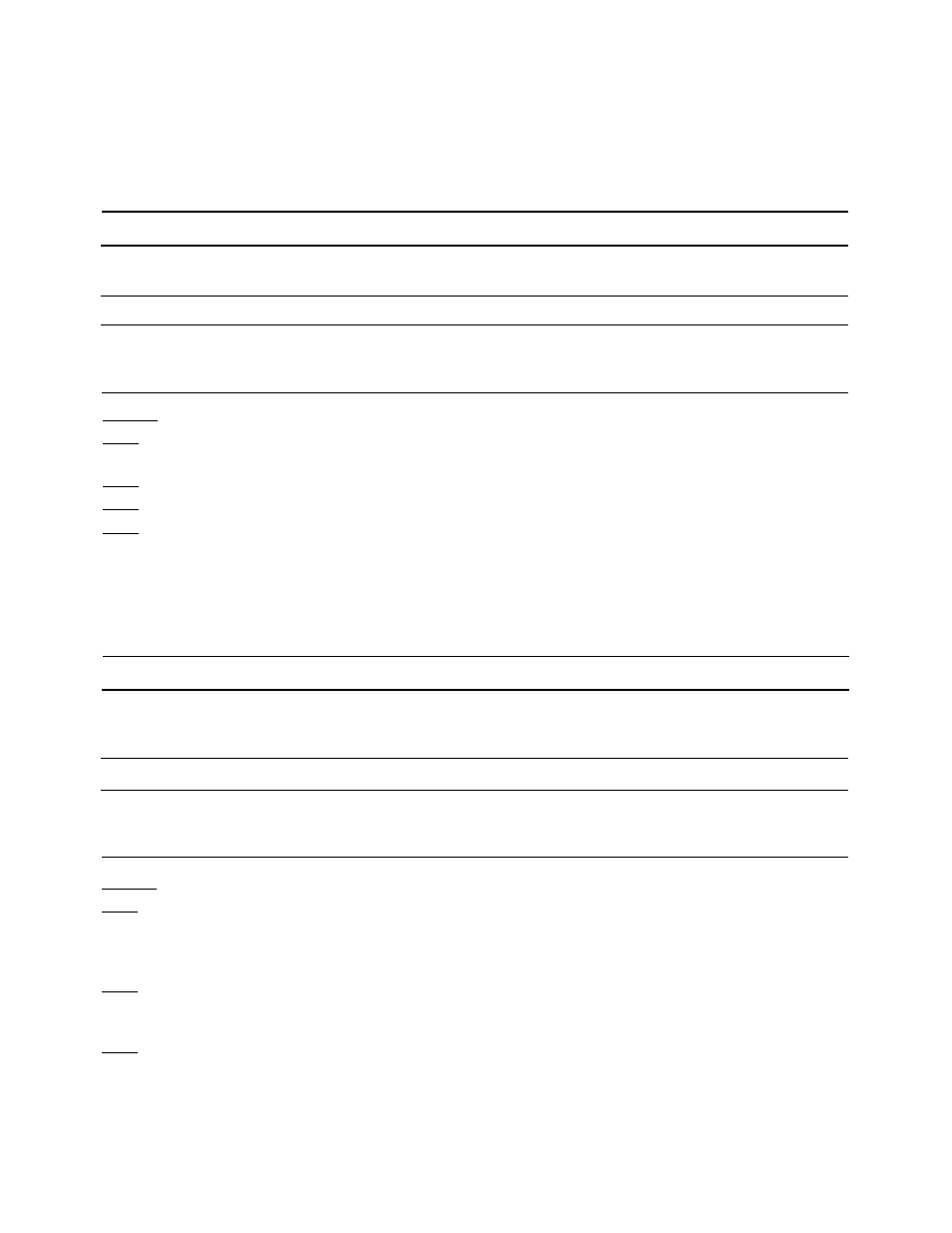

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Bit name

Reserved

Reserved

Reserved

Reserved

LATCH_

Reserved STATE_

GLOBAL_

CNT

RESET

RESET

R/W

—

—

—

—

R/W

—

R/W

WSR

Value

0

0

0

0

0

0

0

0

after

reset

ADDR=0x000: Reset and Performance Latch Control

Bits 7-4: Reserved

Bit 3:

LATCH_CNT

is set to transfer performance monitor counters to registers to read the

counter values.

Bit 2:

STATE_RESET

is set to reset all state machines to the default state.

Bit 1:

Reserved

Bit 0:

GLOBAL_RESET

is set to reset all read/write registers and all state machines.

Note:

GLOBAL_RESET

is self-cleared.

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Bit name

Reserved

Reserved

Reserved

Reserved

Reserved

MII_

SONET_R_

SONET_R_

T_TO_R_

TO_T_LOOP

TO_T_

LOOP

LOOPL

R/W

—

—

—

—

—

R/W

R/W

R/W

Value

0

0

0

0

0

0

0

0

after

reset

ADDR=0x001: Test Modes

Bits 7-3: Reserved

Bit 2:

MII_T_TO_R_LOOP

is set to enable MII loopback mode to perform loopback test. It has the same

function as the MII Management Register in address 0 bit 14 - LOOPBACK. MII TX interface

receives MII TX data, then data is passed directly to MII RX interface and sent to MII RX bus. This

loopback is available in PHY mode only.

Bit 1:

SONET_R_TO_T_LOOP

is set to cause STS-3c/STM-1 data received to be looped to the transmit

SONET/SDH port after passing the framer. It is only allowed when RX_SONETCLK is equal to

TX_SONETCLK.

Bit 0:

SONET_R_TO_T_LOOPL

is set to cause STS-3c/STM-1 data received to be looped to the transmit

SONET/SDH port before passing the framer. It is only allowed when RX_SONETCLK is equal to

TX_SONETCLK.

5.2.1 Common Registers