Agilent Technologies HDMP-3001 User Manual

Page 84

84

TX_MII_FRAMES_REC_OK[23:0]

is the Transmit MII Frames Received OK counter. It is non-resetable

except that a hard or soft reset will clear it. After reaching its max value the counter starts over from zero

again.

This counter is incremented for each frame that was properly byte aligned, did not cause a FIFO error and

was received with the TX_ER inactive. That is, the INFO FIELD TX FIFO Controller checks for EBF and

no FIFO Underrun/Overflow error at the end of a frame to increment this counter.

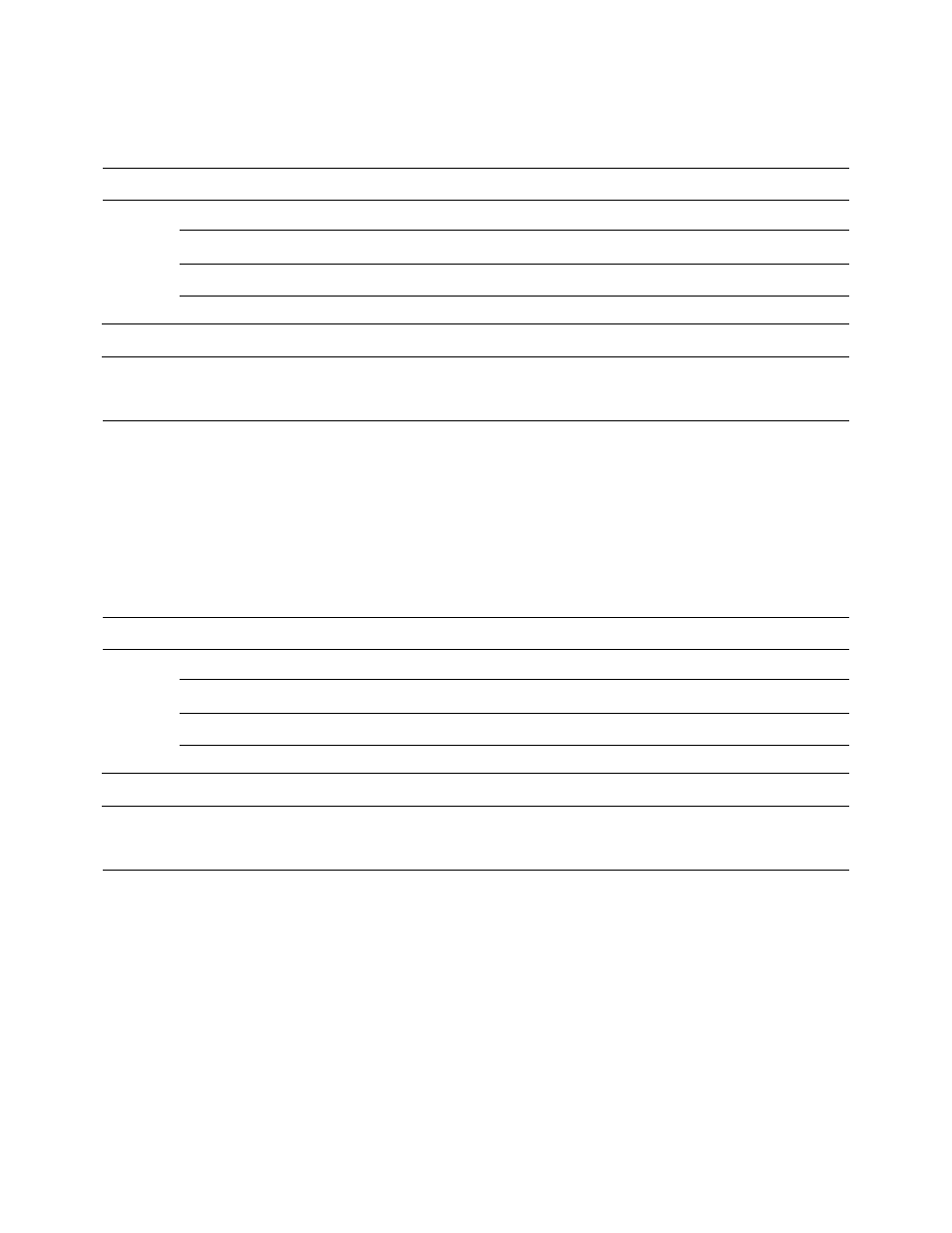

ADDR = 0x18C-F: Transmit MII Frames Received OK Counter

ADDR

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Bit name

0x18C

TX_MII_FRAMES_REC_OK [7:0]

0x18D

TX_MII_FRAMES_REC_OK [15:8]

0x18E

TX_MII_FRAMES_REC_OK [23:16]

0x18F

Fixed 0

R/W

RO

Value

0

after

reset

ADDR = 0x190-0x193: Transmit MII Alignment Error Counter

ADDR

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Bit name

0x190

TX_MII_ALIGN_ERR [7:0]

0x191

TX_MII_ALIGN_ERR [15:8]

0x192

TX_MII_ALIGN_ERR [23:16]

0x193

Fixed 0

R/W

RO

Value

0

after

reset

TX_MII_ALIGN_ERR[23:0]

is the Transmit MII Alignment Error counter. It is non-resetable except that a

hard or soft reset will clear it. After reaching its max value the counter starts over from zero again.

This counter is incremented by frames that contain an odd number of nibbles and do not cause a FIFO error

or a TX_ER error.