Agilent Technologies HDMP-3001 User Manual

Page 19

19

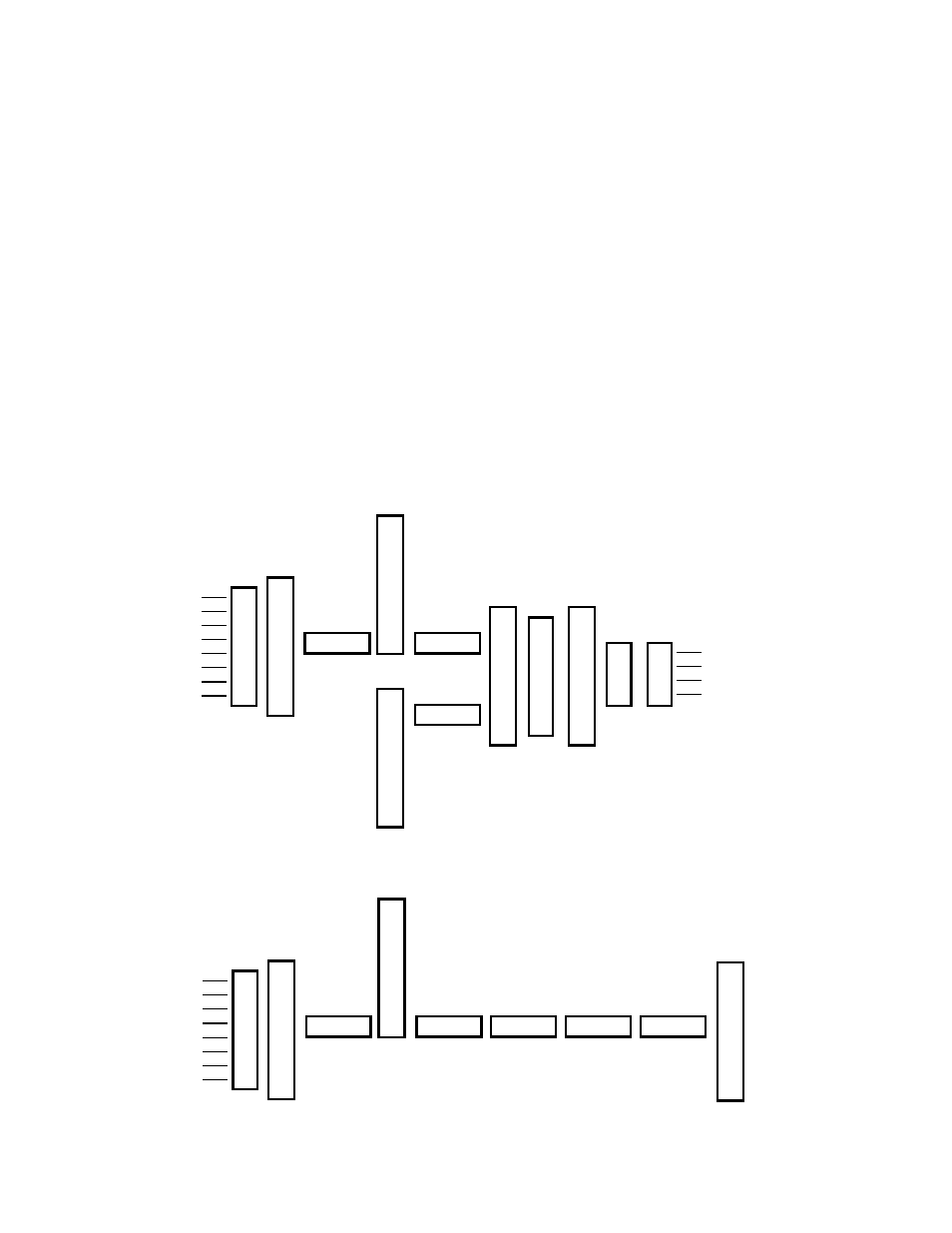

3.4.2 LAPS Mode

In LAPS mode the FCS is calcu-

lated LSB first and the FCS sum is

transmitted in reversed bit order

within each byte. See Figure 6 and

Figure 7.

3.5 Performance Monitoring

For performance monitoring pur-

poses, the HDMP-3001 contains a

number of delta bits, event bits

and error counters.

Delta bits are set by the HDMP-

3001 when a monitored parameter

changes state. The delta bit then

stays high until the controller

TX_DATA[7]

TX_DATA[6]

TX_DATA[5]

TX_DATA[4]

TX_DATA[3]

TX_DATA[2]

TX_DATA[1]

TX_DATA[0]

7

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

0

1

2

3

X

7

S

C

R

L

A

P

S

M

I

I

I

/

F

X

4

3

S

C

R

C

R

C

G

E

N

7 6 5 4 3 2 1 0

F

L

[7]

[0]

7 6 5 4 3 2 1 0

F

L

0 1 2 3 4 5 6 7

F

L

LSN

F

4

5

6

7

MSN

L

PINS

PINS

TXD0

TXD1

TXD2

TXD3

F = FIRST

L = LAST

TX_DATA[7]

TX_DATA[6]

TX_DATA[5]

TX_DATA[4]

TX_DATA[3]

TX_DATA[2]

TX_DATA[1]

TX_DATA[0]

7

6

5

4

3

2

1

0

X

7

S

C

R

X

4

3

S

C

R

C

R

C

G

E

N

7 6 5 4 3 2 1 0

F

L

[7]

[0]

PINS

7 6 5 4 3 2 1 0

F

X

24

X

31

7 6 5 4 3 2 1 0

X

16

X

23

7 6 5 4 3 2 1 0

X

8

X

15

7 6 5 4 3 2 1 0

L

X

0

X

7

Figure 6. LAPS Payload Bit Order

Figure 7. LAPS FCS Bit Order

clears the bit. If a clear occurs si-

multaneously with a parameter

state change, the delta bit remains

set. Delta bits are indicated by a

_D suffix.

When LATCH_CNT in register

0x001 is written from a 0 to a 1, it

produces a pulse on an internal

signal, LATCH_EVENT.

All the internal performance

monitoring counter blocks are

comprised of a running error

counter and a holding register

that presents stable results to the

controller. The counts in all of the

running counters are latched into

the hold registers and the running

counters are cleared when a pulse

occurs on LATCH_EVENT.

To prevent missing a count that

occurs when latching occurs, a

counter is set to one, rather than

zero, if the clear signal is simulta-

neous with an increment. After

being latched, the results are held

to be read by the microprocessor.

The running counters will stop at

their maximum value rather than

roll over to zero.