Agilent Technologies HDMP-3001 User Manual

Page 51

51

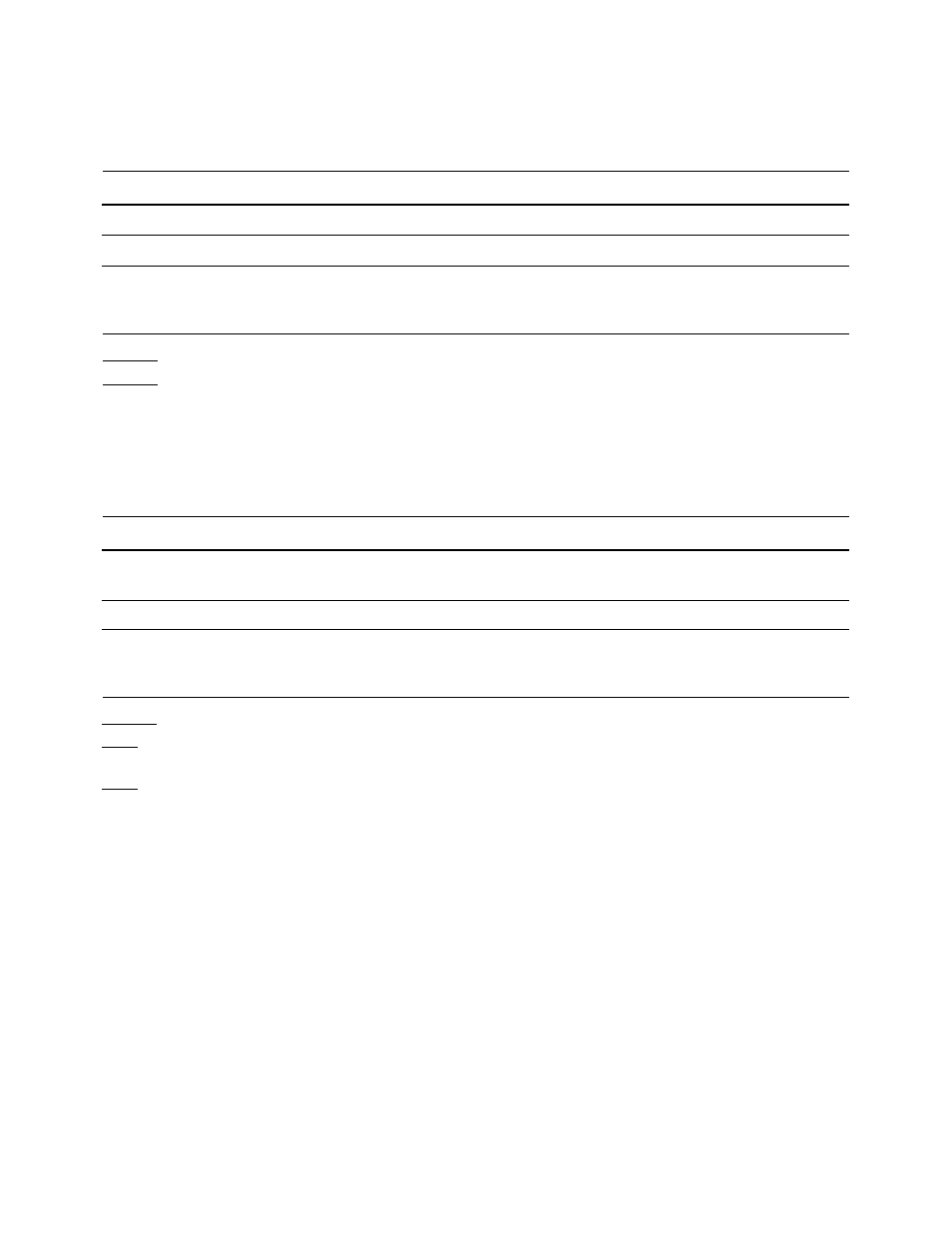

ADDR = 0x005: PHY Address[4:0]

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Bit name

Reserved

Reserved

Reserved

PHY_ADDR[4:0]

R/W

—

—

—

R/W

Value

0

0

0

0x1B

after

reset

Bits 7-5: Reserved

Bits 4-0: PHY_ADDR specifies the PHY address for the HDMP-3001 chip. The chip uses the PHY address to

respond to the Management Entity when addressed through the MDIO port.

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Bit name

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved RX_APS_

SUM_INT

INT

R/W

—

—

—

—

—

—

R

R

Value

0

0

0

0

0

0

0

0

after

reset

ADDR=0x006: Interrupt Status

Bits 7-2: Reserved

Bit 1:

RX_APS_INT

is set to indicate at least one of the RX_K1_D, RX_K2_D, or K1_UNSTAB_D is set

and unmasked. This condition asserts the APS_INT pin unless RX_APS_INT_MASK is set.

Bit 0:

SUM_INT

is set to indicate an active non-masked alarm from a non-masked alarm group. This

condition asserts the INTB pin unless SUM_INT_MASK is set.

List of Interrupt Groups:

TOH_D_SUM, PTR_D_SUM, PATH_D_SUM, and EoS_D_SUM